Einführung in die Quartus Synthesesoftware

Quartus ist die Synthesesoftware der Firma Altera, mit der eine Schaltungsbeschreibung in VHDL in eine Belegungsdatei für ein FPGA übersetzt werden kann. Ein FPGA ist ein programmierbarer Baustein, dessen Funktion durch eine Belegungsdatei festgelegt werden kann. Starten Sie Quartus.

Linux: Wechseln Sie in das Verzeichnis „first“ und starten Sie mit „quartus“.

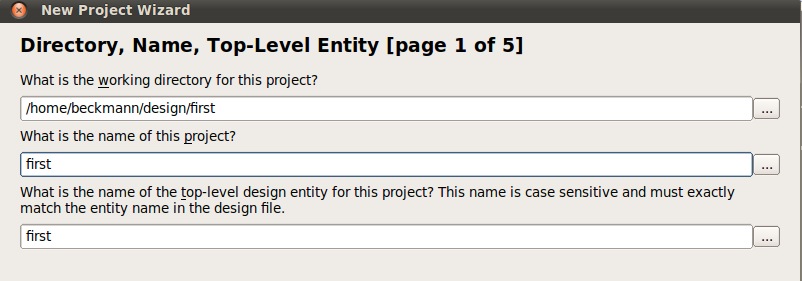

Klicken Sie auf „Create a New Project“. Geben Sie als Projektnamen und Entitynamen „first“ an.

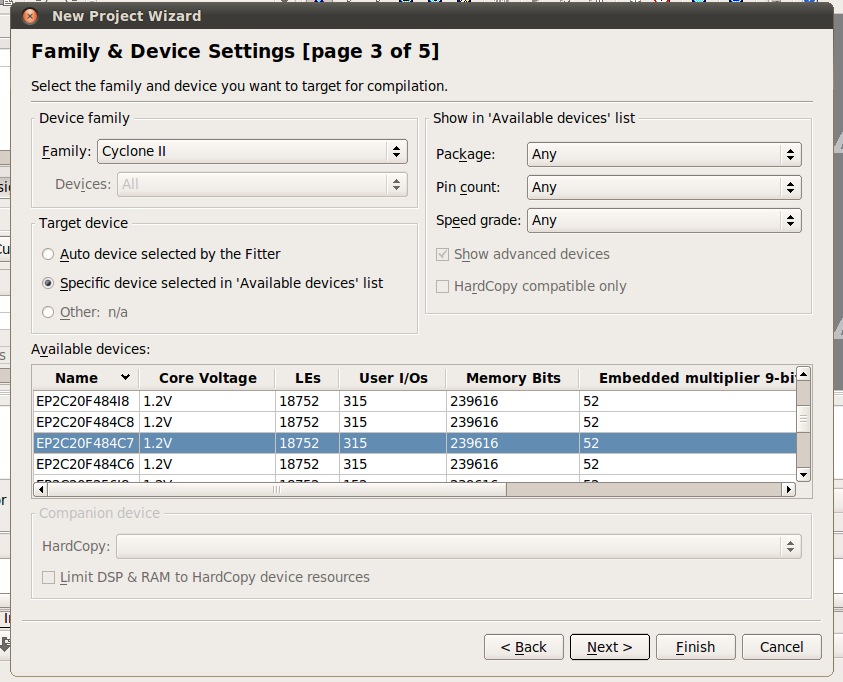

Fügen Sie die Datei „first.vhd“ dem Projekt hinzu. Die Datei „first_tb.vhd“ gehört nicht zum Projekt, da diese Datei nur die Testumgebung für die Simulation enthält. Wählen Sie als „Device Family“ Cyclone II und als Device EP2C20F484C7. Dies ist der Baustein auf dem verwendeten Terasic DE01 Board.

Danach mit „Finish“ den Wizard verlassen.

Die Belegung für den FPGA Baustein kann jetzt aus der VHDL Beschreibung synthetisiert werden. Allerdings fehlt noch die Zuordnung wie die Ein- und Ausgangspins des Moduls „first“ mit den Pins des FPGA verbunden werden sollen. In dem Beispiel „first“ werden die Namen „SW“ und „LEDR“ verwendet, die auf dem Terasic DE1 Board für die Schalter und die Leuchtdioden verwendet werden. Die Zuordnung von Signalnamen zu FPGA Pins erfolgt über eine Tabelle.

Lesen Sie die Tabelle ein mit „Assignments→Import Assignments“ und wählen Sie dort die Datei „DE1_pin_assignments.csv“. Mit „Assignments→Pin Planner“ können Sie die Zuordnung anschauen. Man kann beispielsweise erkennen, dass das Signal LEDR[9] dem Pin „PIN_R17“ zugeordnet ist.

Da bei unserem Entwurf nicht alle Pins des FPGA verwendet werden, die Pins allerdings auf dem FPGA angeschlossen sind, müssen alle nicht verwendeten Pins als Eingang geschaltet werden. Sie können dies in „Assignments→Device“ und dann über den Schalter „Device and Pin Options“ einstellen. Wählen Sie dort für „Unused Pins“ : „As input tri-stated“.

Über „Processing→Start Compilation“ können Sie jetzt die Synthese starten.