## Aufgabe 1

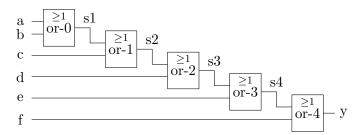

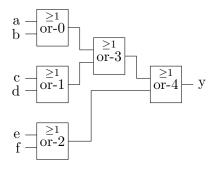

Die in Abbildung 1 dargestellte Schaltung ist aus Oder Gattern aufgebaut. Jedes dieser Gatter hat eine Verzögerungszeit von  $t_{pd}=5ns$ . Die Verzögerung ist für steigende und fallende Signale gleich  $(t_{pdlh}=t_{pdhl})$ .

Abbildung 1: Verschaltung von fünf ODER Gattern

- a) Zeichnen Sie den Timingpfad mit der maximalen Verzögerung in die Schaltung ein.

- b) Zeichnen Sie den Timingpfad mit der minimalen Verzögerung in die Schaltung ein.

- c) Geben Sie die maximale und die minimale Verzögerungszeit an.

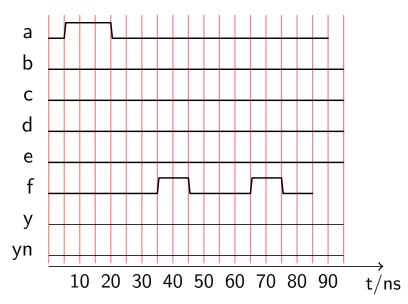

- d) In Abbildung 2 ist ein beispielhafter Verlauf der Eingangssignale dargestellt. Zeichnen Sie den zeitlichen Verlauf des Signals am Ausgang y für die Schaltung gemäß Abbildung 1 in die Abbildung 2 ein. Das Signal yn wird für die Aufgabe f) benötigt.

Abbildung 2: Zeitverlauf der Eingangssignale

- e) Ändern Sie die Verschaltung der Gatter derart, dass die Funktion der Schaltung sich nicht ändert, aber die maximale Verzögerungszeit minimiert wird. Geben Sie für die neue Schaltung die maximale und die minimale Verzögerungszeit an. Beweisen Sie mit Hilfe der booleschen Theoreme, dass die Funktion der Schaltung gleich geblieben ist.

- f) Zeichnen Sie den zeitlichen Verlauf des Signals am Ausgang y der neuen Schaltung aus Aufgabe e) in Abbildung 2 ein.

Lösung

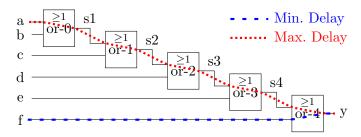

a) und b) In Abbildung 3 sind die Pfade für die maximale und die minimale Verzögerung eingezeichnet. Die Gesamtverzögerung wird durch die Verzögerung der einzelnen Gatter auf dem Pfad bestimmt. In diesem Beispiel mit gleichen Verzögerungszeiten für alle Gatter, ist der Pfad, der von irgendeinem Eingang a,b,c,d,e,f zum Ausgang y durch die größtmögliche Anzahl von Gattern läuft, der Pfad mit der maximalen Verzögerung. Die minimale Verzögerung ergibt sich für den Pfad, der von irgendeinem Eingang durch die geringst mögliche Anzahl von Gattern zum Ausgang y führt. Das ist der Pfad f-y. Die beiden Pfade a-y und b-y haben beide eine gleich lange maximale Verzögerung. Dargestellt ist nur der Pfad a-y.

Abbildung 3: Timingpfade für minimale und maximale Verzögerung

- c) Die maximale Verzögerung für den Pfad a-f oder b-f ergibt sich durch die Summe der Verzögerungszeiten der Gatter or-0 bis or-4 von jeweils 5ns zu  $5 \cdot 5ns = 25ns$ . Die minimale Verzögerung ist durch or-4 mit 5ns gegeben.

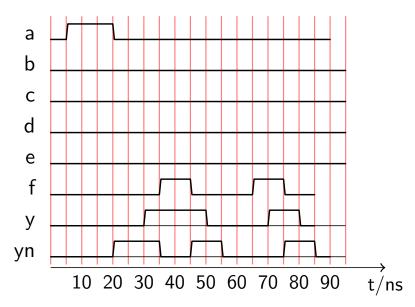

- d) und f) In Abbildung 4 ist der zeitliche Verlauf des Signals am Ausgang y dargestellt. yn zeigt den Signalverlauf der Schaltung aus der folgenden Aufgabe gemäß Aufgabenstellung f). Durch die logische ODER Funktion der Schaltung führt eine 0 an einem der Eingänge zu einer 1 am Ausgang. Zunächst ändert sich der Eingang a von 0 auf 1. Eine Änderung ist fünf Gatterlaufzeiten, d.h. 25ns nach dieser Änderung am Ausgang y sichtbar. Die Dauer des Pulses am Eingang a beträgt 15 ns. Eine Änderung am Eingang f ist mit einer Verzögerung von einer Gatterlaufzeit am Ausgang y sichtbar. Deshalb bleibt der Ausgang y auch für insgesamt 20ns auf 1.

Abbildung 4: Zeitverlauf des Signals am Ausgang v aus Aufgabe d) und yn aus Aufgabe f)

e) Die in Abbildung 1 dargestellte Schaltung hat die logische Funktion (1).

$$y = ((((a+b)+c)+d)+e)+f$$

(1)

Für die ODER Verknüpfung gilt das Assoziativgesetz. Die Klammern im Ausdruck (1) können deshalb anders gesetzt werden. Gleichung (2) unterscheidet sich von Gleichung (1) nur durch eine andere Klammerung und deshalb sind die Funktionen (1) und (2) äquivalent.

$$y = ((a+b) + (c+d)) + (e+f)$$

(2)

Diese Funktion (2) führt in einer direkten schaltungstechnischen Realisierung zu einer Baumstruktur wie in Abbildung 5 dargestellt.

Abbildung 5: Schaltung als Baumstruktur

Die maximale Laufzeit ist jetzt durch drei Gatterlaufzeiten gegeben und hat sich deshalb auf 15 ns reduziert. Die minimale Gatterlaufzeit ist auf zwei Gatterlaufzeiten angestiegen.

## Aufgabe 2

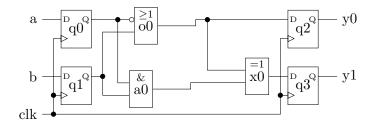

In Abbildung 6 ist eine sequentielle Schaltung mit Flipflops und kombinatorischen Elementen dargestellt.

Abbildung 6: Schaltung mit Flipflops und Kombinatorik

Für diese Schaltung soll das Timingverhalten untersucht werden. Die folgenden Timingparameter beschreiben die Schaltungskomponenten:

$$t_{pd} = 0.9 \,\mathrm{ns}, t_{co} = 0.5 \,\mathrm{ns}, t_{su} = 0.7 \,\mathrm{ns}, t_h = 2 \,\mathrm{ns}$$

Die Verzögerungszeit ist für alle kombinatorischen Gatter gleich und unabhängig davon, ob das Ausgangssignal steigt oder fällt. Der Takt wird als ideal betrachtet und kommt gleichzeitig an den Takteingängen von allen Flipflops an. Die Taktfrequenz beträgt 100 MHz. Die Eingänge a und b

der Schaltung sind synchron zum Takt. Der Timingverhalten der Signale an den Eingängen a und b soll nicht betrachtet werden.

- a) Der Taktfrequenz der Schaltung soll erhöht werden. Berechnen Sie die maximale Taktfrequenz mit der die Schaltung betrieben werden kann.

- b) Prüfen Sie, ob es zu Timingverletzungen im Betrieb der Schaltung kommen kann. Welche Timingbedingung ist verletzt?

- c) Geben Sie eine Signalfolge für die Eingänge a und b an, bei der das Timingproblem an einem der Ausgänge sichtbar wird. Zeichnen Sie ein Timingdiagramm, in dem die Zusammenhänge deutlich werden. Welche Folgen hat die Timingverletzung?

- d) Verändern und erweitern Sie den kombinatorischen Teil der Schaltung mit Invertern um das Timingproblem zu lösen. Ein Inverter hat eine Verzögerungszeit von  $t_{pd} = 0.4 \,\mathrm{ns}$ . Die Taktleitung soll unverändert bleiben.

- e) Wie groß ist die maximale Taktfrequenz der veränderten Schaltung?

## Lösung

a) Die Daten, die an den Flipflops q0 und q1 mit der steigenden Taktflanke starten, müssen rechtzeitig vor der nächsten Taktflanke stabil an den Dateneingängen D der Flipflops q2 und q3 anliegen. Dabei muss die Setupzeit  $t_{su}$  der Flipflops berücksichtigt werden, d.h. die Daten müssen  $t_{su}$  vor der nächsten steigenden Taktflanke stabil sein. Die Zeit bis zu der die Daten stabil sind, ergibt sich aus der Verzögerungszeit im kombinatorischen Teil der Schaltung und aus der Verzögerung der Daten im Flipflop (Clock to Output Delay  $t_{co}$ ).

Die Verzögerung der Daten in den Flipflops und die Setupzeit der Flipflops  $t_{su}$  ist bei allen Flipflops gleich. Auch der Takt kommt an allen Flipflops zum gleichen Zeitpunkt an. Deshalb ist hier nur der Timingpfad mit der längsten Verzögerung im kombinatorischen Teil bestimmend für die maximal mögliche Taktfrequenz  $fmax_{clk}$ .

Die maximale Verzögerung im kombinatorischen Teil der Schaltung  $tcomb_{dmax}$  ergibt sich auf den Pfaden durch das UND Gatter a0 und das XOR Gatter x0. Die maximale Verzögerungszeit durch Kombinatorik ist deshalb  $tcomb_{dmax} = 2 \cdot t_{pd}$ . Die Pfade, die die maximale Frequenz bestimmen sind  $clk \to q0 \to a0 \to x0 \to q3$  und  $clk \to q1 \to a0 \to x0 \to q3$ . Die Verzögerung ist auf diesen Pfaden gleich lang. Die maximale Frequenz ergibt sich gemäß Gleichung 4 zu 333 MHz.

$$1/f max_{clk} = tp_{clk} = t_{co} + tcomb_{dmax} + t_{su} = t_{co} + 2 \cdot t_{pd} + t_{su} = 3 \text{ ns}$$

(3)

$$\Rightarrow f max_{clk} = 1/t p_{clk} = 1/3 \text{ ns} = 333 \text{ MHz}$$

(4)

- b) Bei dieser Schaltung gibt es eine Holdzeitverletzung an Flipflop q2. Die Holdzeit der Flipflops  $t_h$  wird verletzt, weil Daten am Eingang D von Flipflop q2 nach der steigenden Taktflanke nicht lange genug stabil sind. Die Verzögerung der Daten ist gegeben durch  $t_{co}$  und die Verzögerung in der Kombinatorik, die hier durch das ODER Gatter gegeben ist. Die Gesamtverzögerung beträgt also  $t_d = t_{co} + t_{com}b_d = 0.5 \,\mathrm{ns} + 0.9 \,\mathrm{ns} = 1.4 \,\mathrm{ns}$ . Die Holdzeit des Flipflops beträgt aber  $t_h = 2 \,\mathrm{ns}$  und ist deshalb verletzt. Am Flipflop q3 kommt es zu keiner Holdzeitverletzung, da die Verzögerung der Daten dort durch den längeren kombinatorischen Pfad 2.3 ns beträgt.

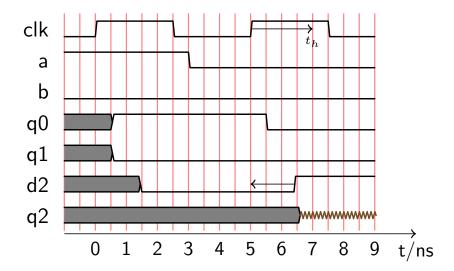

- c) Um das Problem sichtbar zu machen, müssen sich die Daten d2 am Eingang D des Flipflops q2 ändern. Die Daten am Eingang D hängen von den Ausgängen der Flipflops q0 und q2 gemäß der folgenden logischen Gleichung ab: d2 = q0' + q1. Ein Signalwechsel von 0 nach 1 kann mit der Sequenz (a,b) = (1,0),(0,0) erzeugt werden.

Abbildung 7: Holdviolation

In Abbildung 7 ist der zeitliche Verlauf der Signale mit der Holdverletzung dargestellt. Die Taktfrequenz in der Darstellung beträgt 200 MHz. Das Signal d2 am D Eingang des Flipflops q2 ändert sich 1.4 ns nach der steigenden Taktflanke innerhalb der Holdzeit des Flipflops.

Durch die Signaländerung innerhalb der Holdzeit des Flipflops kann das Flipflop in den metastabilen Zustand kommen. Das Verhalten der Schaltung lässt sich dann nicht mehr vorhersagen.

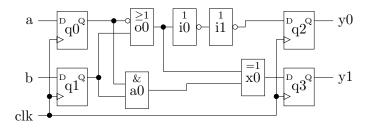

d) Um die Holdzeitverletzung zu verhindern, kann man das Signal am D Eingang von q2 durch zusätzliche Inverter im Pfad zusätzlich verzögern. Dabei müssen die Inverter paarweise eingesetzt werden um die Funktion der Schaltung nicht zu ändern. In Abbildung 8 sind zwei zusätzliche Inverter eingezeichnet.

Abbildung 8: Schaltung mit zusätzlichen Invertern zur Verhinderung der Holdverletzung

Jeder Inverter hat eine Verzögerungszeit von 0.4 ns. Deshalb erhöht sich die gesamte Zeit bis zur Änderung der Daten von 1.4 ns auf 2.2ns. Die Holdzeitverletzung ist mit dieser Verzögerung nicht mehr möglich.

e) Durch die zusätzlichen Inverter hat sich die Verzögerung auf den Timingpfaden zum Flipflop q2 erhöht. Allerdings ist die Verzögerung immer noch geringer als die Verzögerung auf dem bisherigen längsten Pfad. Deshalb ändert sich an der maximalen Frequenz der Schaltung nichts.