Digitaltechnik Praktikum - Einführung Quartus

In diesem Tutorial lernen Sie die FPGA Synthesesoftware Quartus von Altera kennen. Das Ziel ist es das FPGA so zu konfigurieren, dass mit Hilfe der Schalter SW die roten Leuchtdioden LEDR ein- und ausgeschaltet werden können. Sie lernen drei Varianten zum Aufsetzen eines Quartusprojektes kennen

- Manuelles Aufsetzen eines Quartusprojektes mit Hilfe des Assistenten.

- Aufsetzen und Synthese mit eine tcl Skript.

- Synthese auf Basis von Makefiles

Dabei wird in den folgenden Versuchen nur die Synthese mit Hilfe von Makefiles verwendet. Allerdings verwenden Sie die grafische Benutzeroberfläche der Software “Quartus” auch um beispielsweise einen Schaltplan anzuzeigen.

Vorbereitung

Im User Manual für das Altera DE1 Board finden Sie auf den Seiten 24 bis 27 eine Beschreibung der LEDs, der Schalter SW und der Taster KEYS. Im Schaltplan des DE1 Boards können Sie nachschauen an welchen Pins die LEDs und die Schalter angeschlossen sind. Diese Anschlüsse sind auch im Handbuch in Tabellen 4.1 bis 4.3 angegeben. Beispielsweise ist LEDR0 an Pin R20 des FPGA angeschlossen. Auf der CDROM, die zu dem Altera DE1 Board gehört, befindet sich eine Tabelle DE1_pin_assignments.csv, in denen diese Zuordnung von Signalnamen wie LEDR0 zu den Pins des FPGA aufgeführt ist.

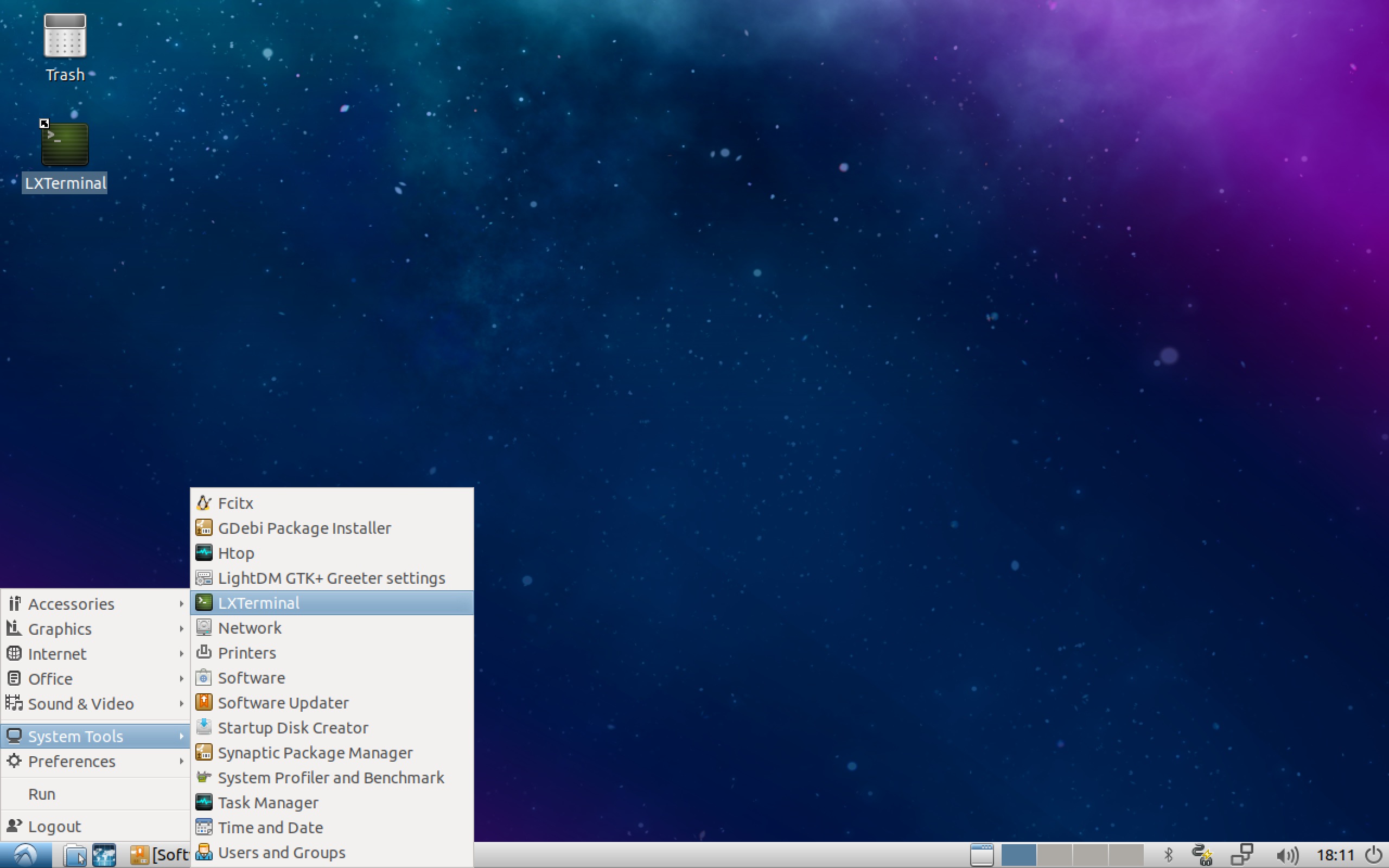

Starten einer Shell unter Ubuntu

Starten Sie das Terminal über das Menu “System Tools → LX Terminal”.

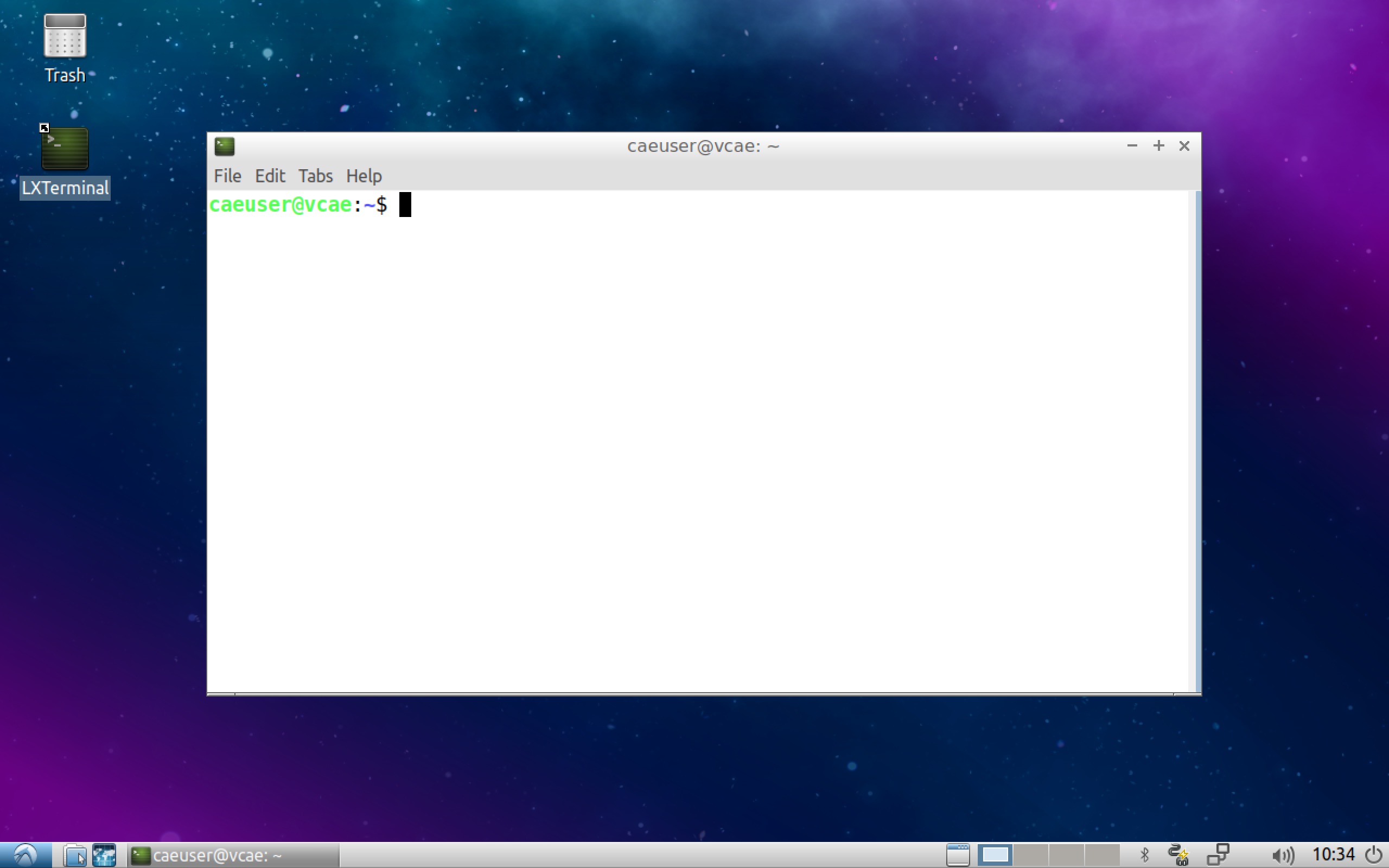

Jetzt haben Sie ein geöffnetes Terminalprogramm.

Überblick über einige Unix Shellbefehle

| Befehl | Beispiel | Beschreibung |

|---|---|---|

| ls | ls -la | Anzeige der Dateien im aktuellen Verzeichnis |

| pwd | pwd | Anzeige des Pfads vom aktuellen Verzeichnis |

| mkdir | mkdir projects | Erzeugen eines neuen Verzeichnisses “projects” |

| cd | cd projects | Wechsel in das Verzeichnis “projects” |

| cd | cd .. | Wechsel in das höhere Verzeichnis ausgehend vom aktuellen Verzeichnis |

| man | man ls | Aufruf des Handbuchs für den Befehl “ls” |

| rm | rm hallo.txt | Löschen der Datei “hallo.txt” |

| less | less hallo.txt | Anschauen der Datei “hallo.txt”. Beenden mit “q” |

| vi | vi hallo.txt | Editor starten für die Datei hallo.txt |

Laden der Designdaten vom git Server

Die Designdaten für das Digitaltechnikpraktikum sind auf dem git Server der Fakultät Elektrotechnik. Der Zugriff erfolgt über das git Programm. Auf dem git server befindet sich das Projekt Digitaltechnikpraktikum mit den Dateien für das Praktikum.

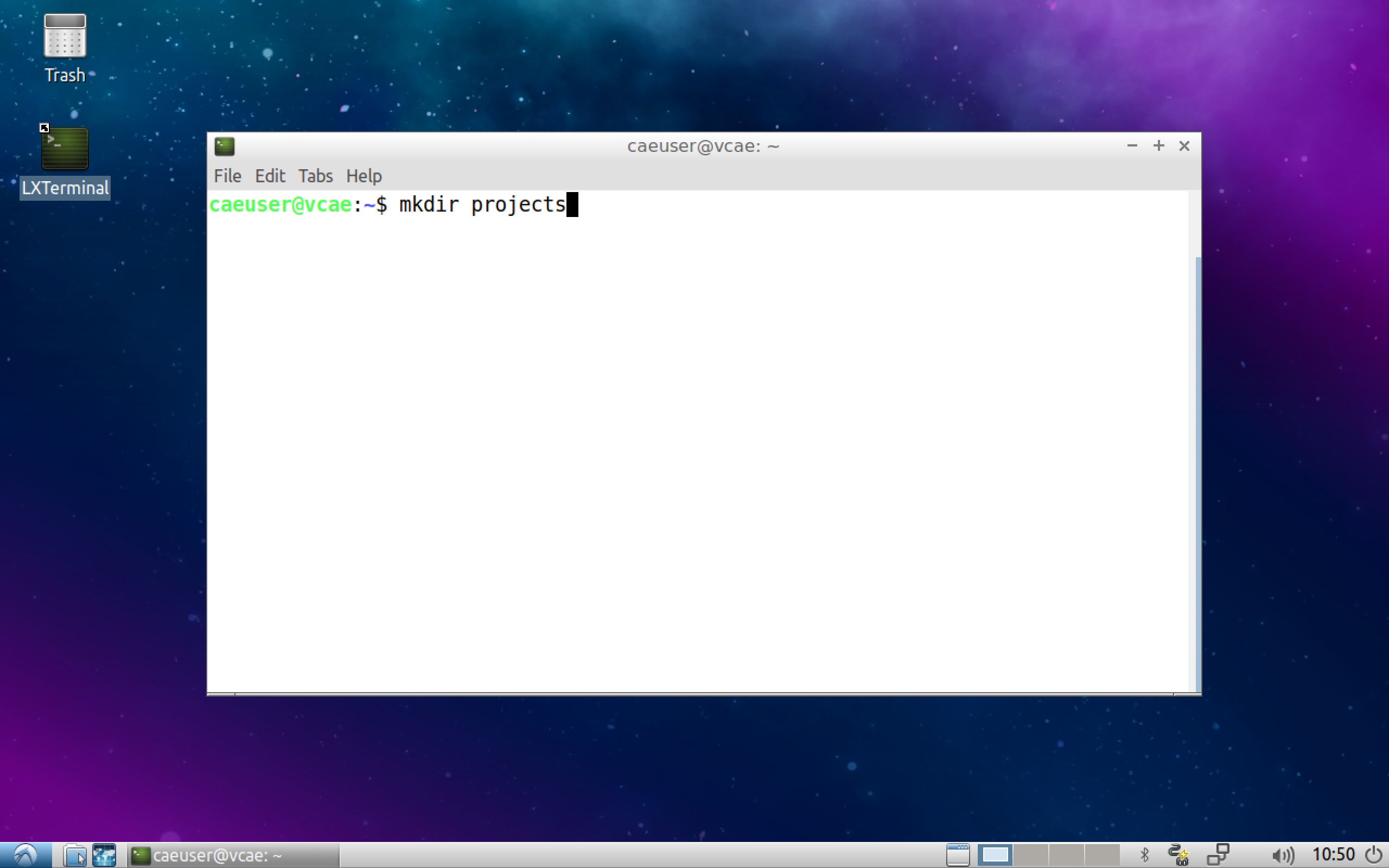

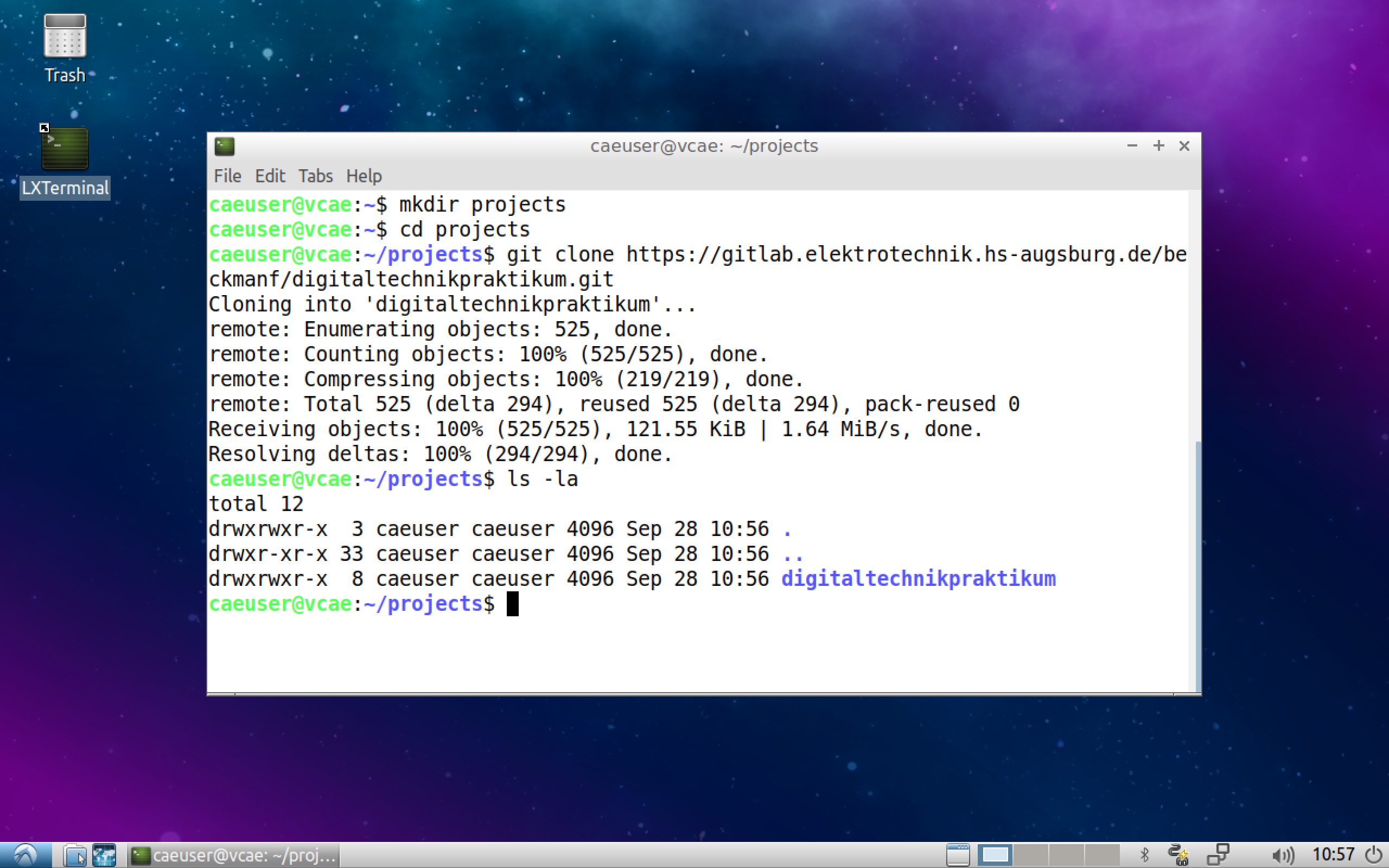

Richten Sie ein Verzeichnis “projects” in Ihrem home directory ein. Das Homedirectory ist “/home/caeuser”. Wechseln Sie in das Verzeichnis “projects” und laden Sie mit “git” die Designdaten vom git Server.

mkdir projects cd projects git clone https://gitlab.elektrotechnik.hs-augsburg.de/beckmanf/digitaltechnikpraktikum.git ls -la

Das sollte dann so aussehen:

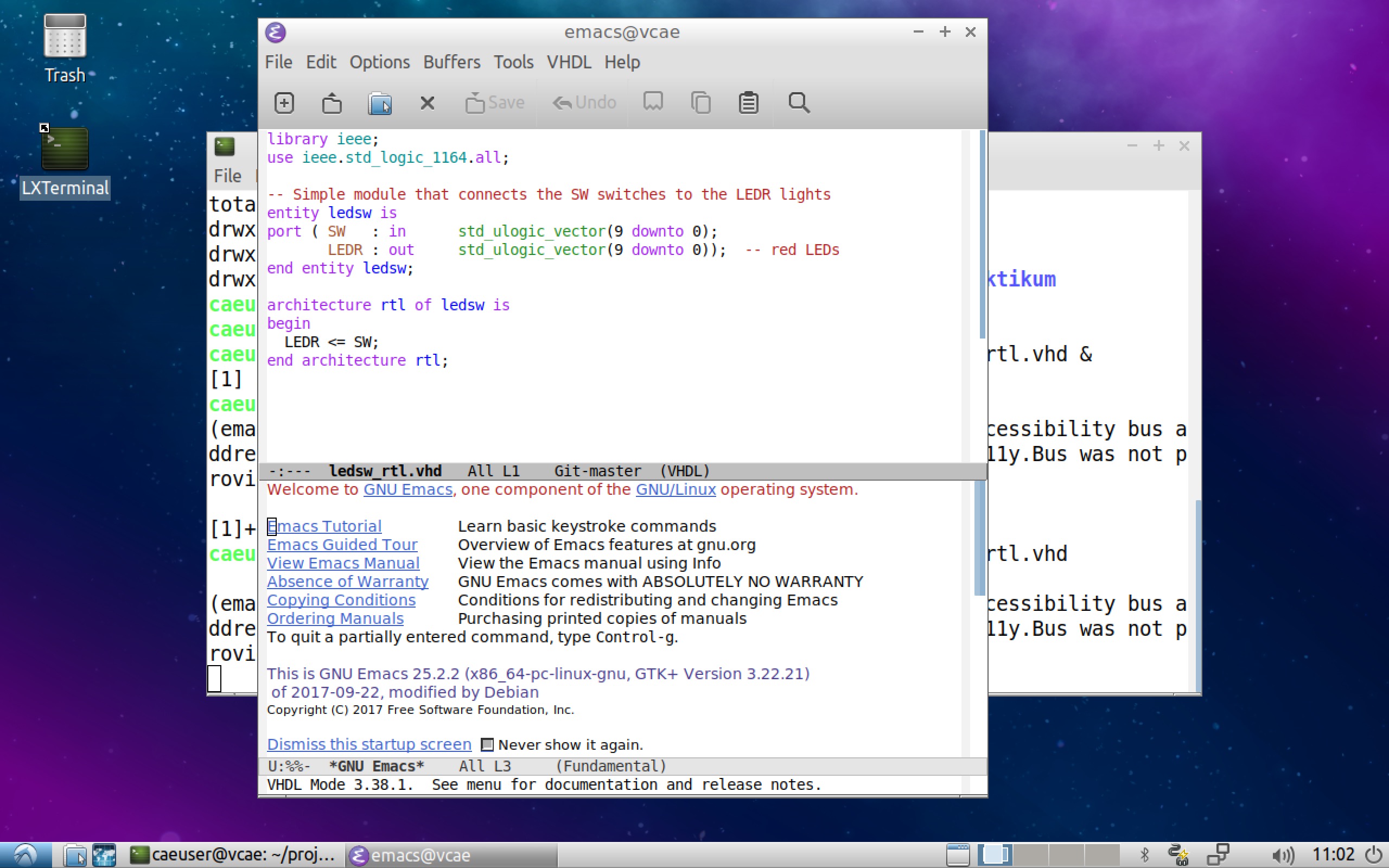

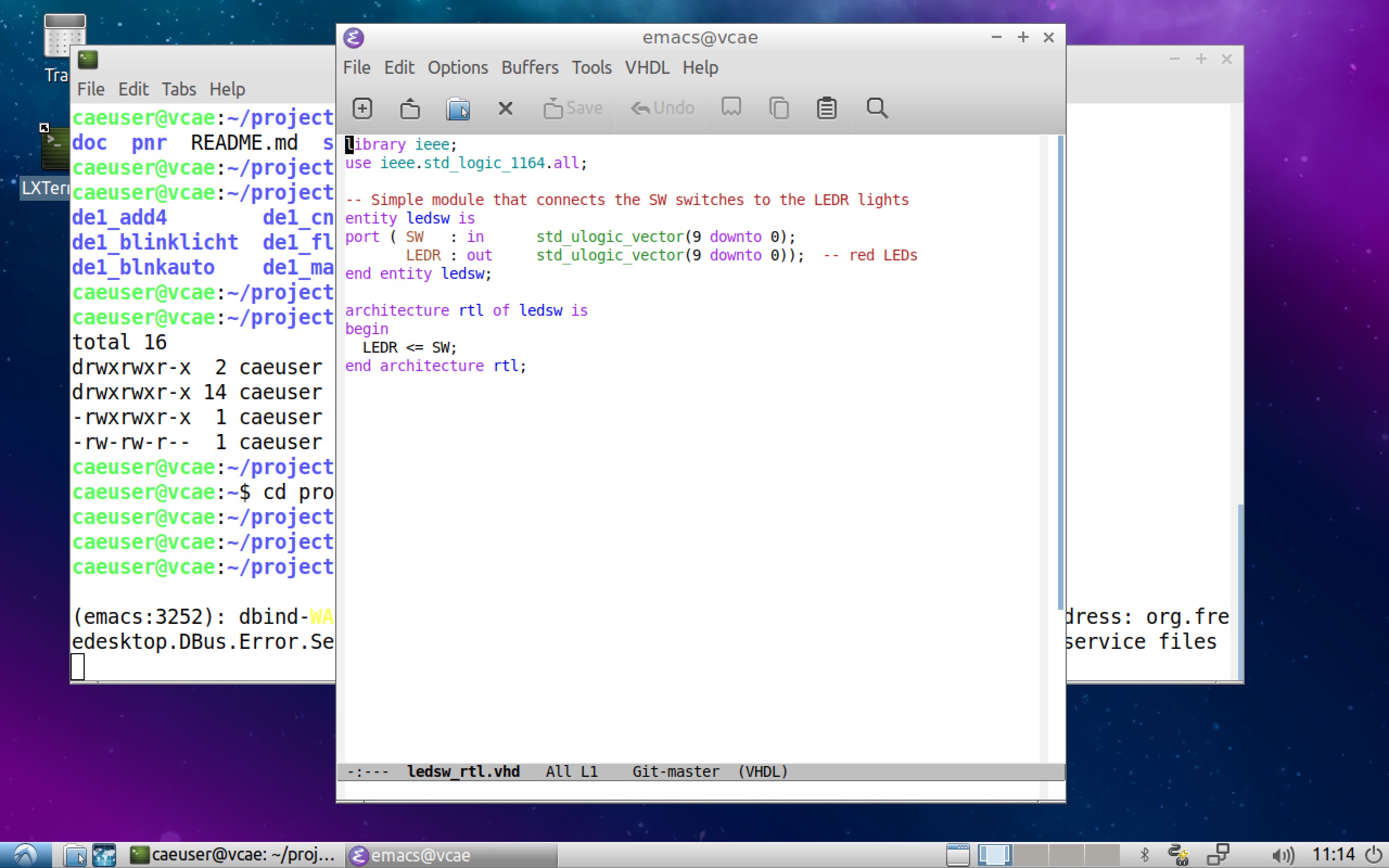

Wechseln sie dann in das Verzeichnis “digitaltechnikpraktikum” und dann in das Verzeichnis “src”. Starten Sie dort einen Editor und schauen sich die Datei “ledsw_rtl.vhd” an.

cd digitaltechnikpraktikum cd src ls -la emacs ledsw_rtl.vhd

Im Emacs Editor werden nach dem Start zwei “Buffer” angezeigt. Tippen Sie

ctrl-x 1

um nur den Buffer mit der VHDL Datei anzuzeigen.

Die VHDL Datei beschreibt ein Design mit 10 Eingängen “SW” und 10 Ausgängen “LEDR”. In der Architektur werden die Eingänge “SW” auf die Ausgänge “LEDR” geschaltet. Damit sollen die roten LEDs abhängig von den Schaltern “SW” ein- und ausgeschaltet werden.

Synthese mit Altera Quartus - Manuelles Aufsetzen des Projektes

Im ersten Anlauf wird das Projekt manuell mit Hilfe des Assistenten aufgesetzt. Im Projekt gibt es ein Verzeichnis “pnr”. Dieser Name steht für “Place And Route” und umfasst die Designdaten für die Synthese einer Schaltung für das FPGA. Wechseln Sie in das Verzeichnis “ledsw-manual”.

cd cd projects cd digitaltechnikpraktikum cd pnr cd ledsw-manual

In diesem Verzeichnis befindet sich eine Datei “ledsw_pin_assignments.csv”. Diese Datei enthält die Pinkonfiguration für die Schalter “SW” und die Leuchtdioden “LEDR” Sie können sich die Datei mit

less ledsw_pin_assignments.csv

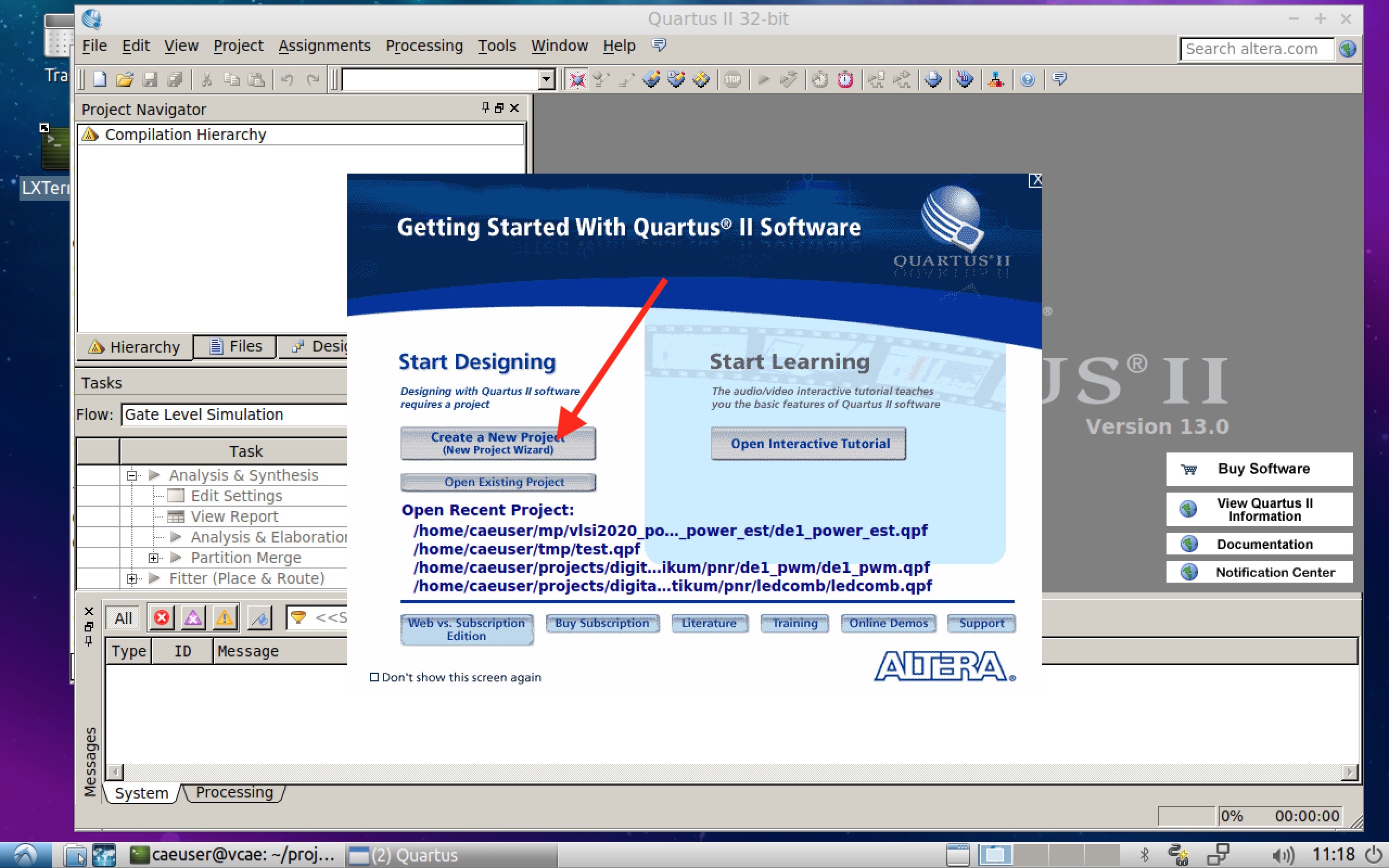

anschauen. Zum Verlassen von “less” drücken Sie “q”. Starten Sie jetzt die Altera Quartus Software mit “quartus”

quartus

Es erscheint folgendes Fenster.

Drücken Sie “Create a new project”.

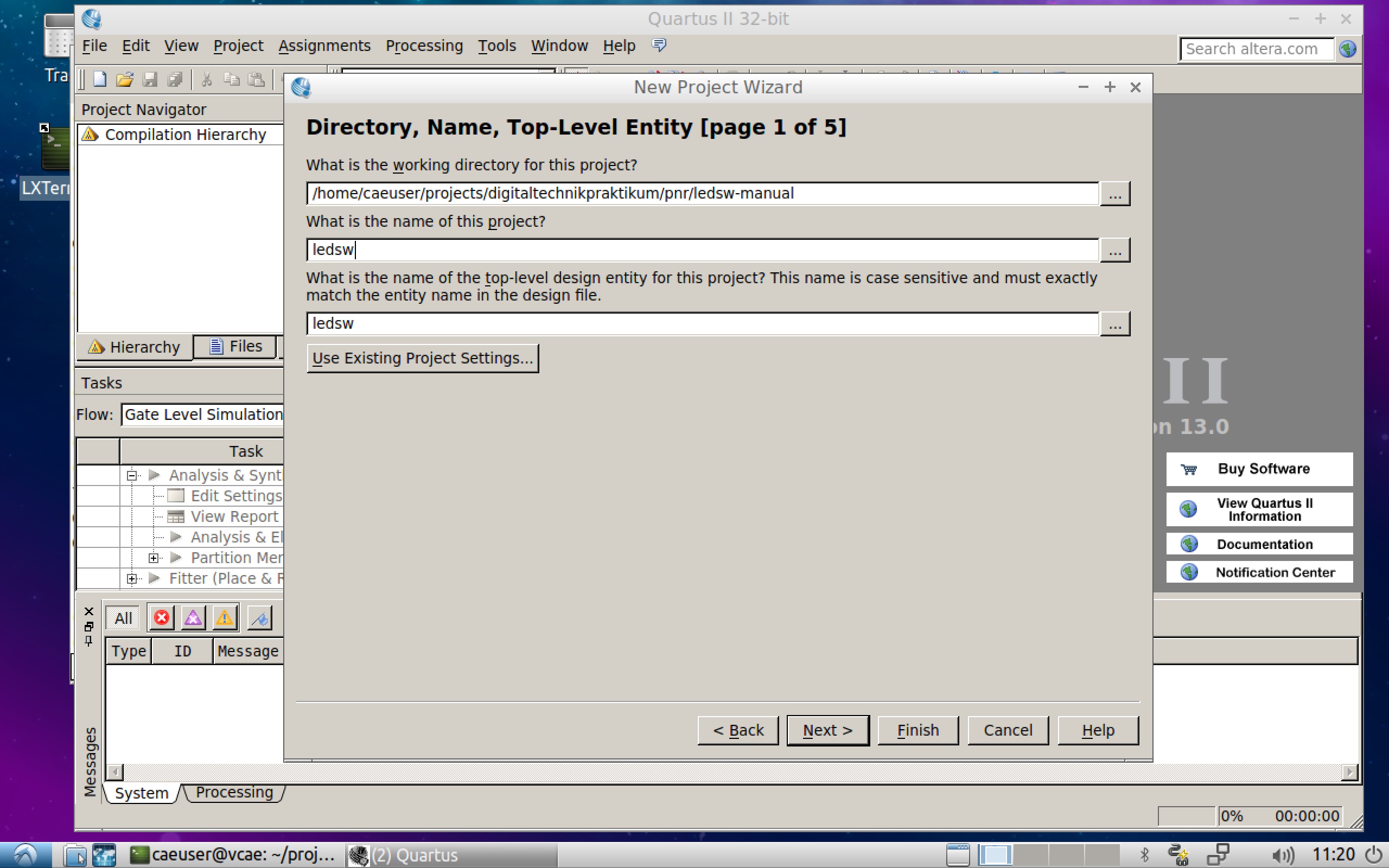

Wählen Sie als Projektnamen “ledsw” und als Namen für die Toplevelentity auch “ledsw”. Achten Sie darauf, dass das working directory “digitaltechnikpraktikum/pnr/ledsw-manual” ist. In diesem Verzeichnis werden die (u.a. temporäre) Projektdateien gespeichert.

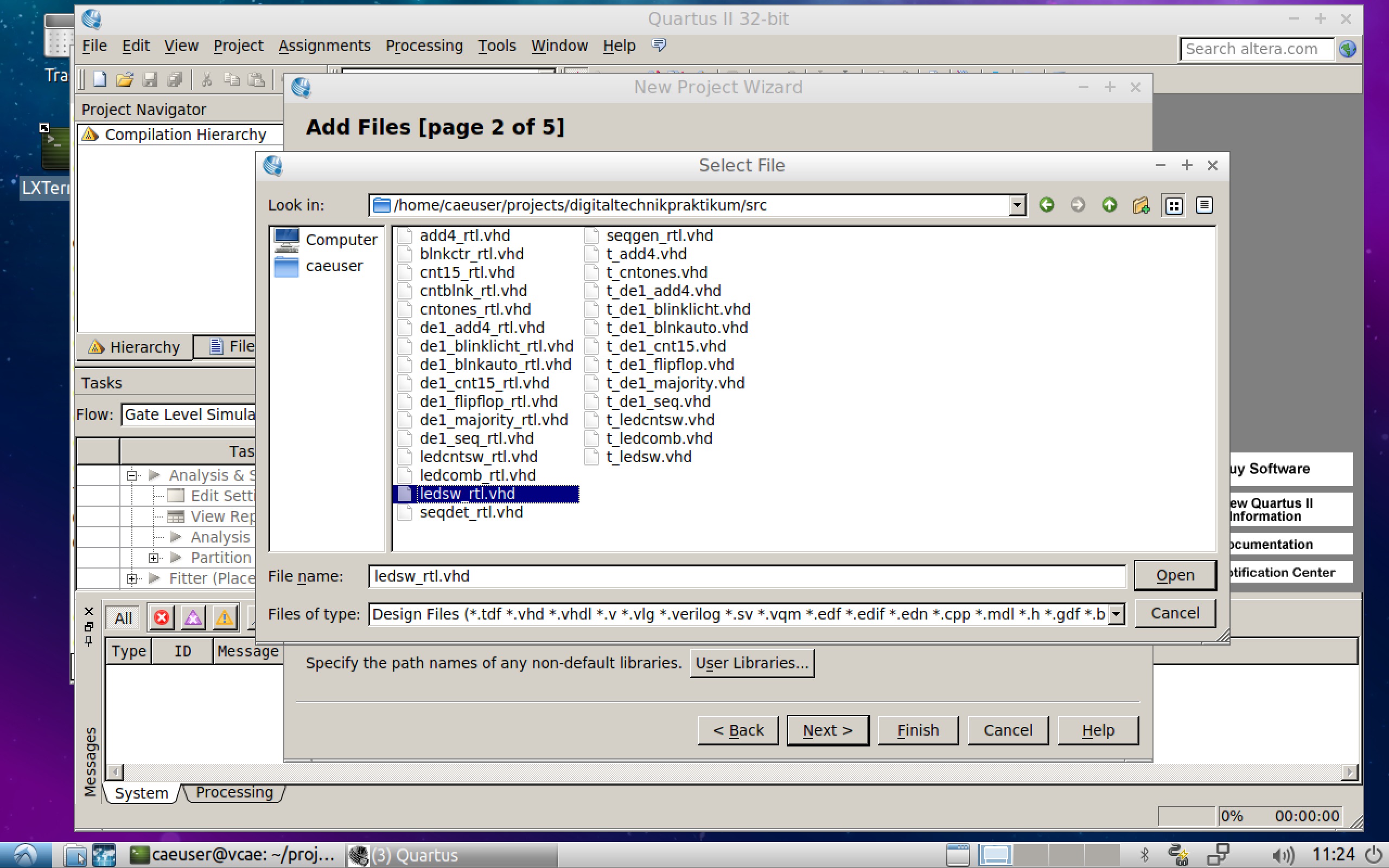

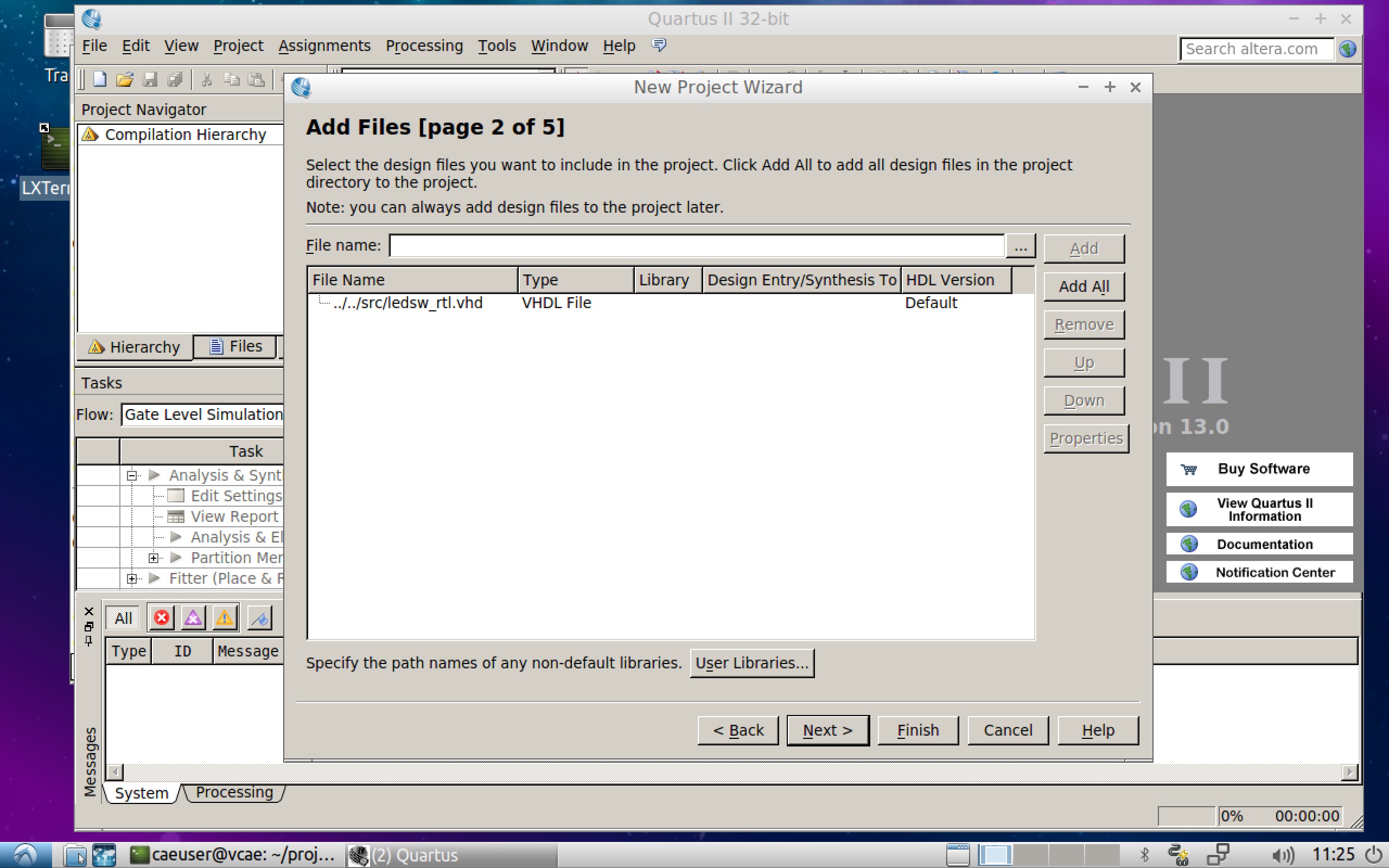

Im nächsten Schritt müssen dem Projekt die VHDL Dateien hinzugefügt werden. In diesem Projekt gibt es nur die eine Datei “ledsw_rtl.vhd”. Wählen Sie die Datei aus und klicken Sie auf “ADD”.

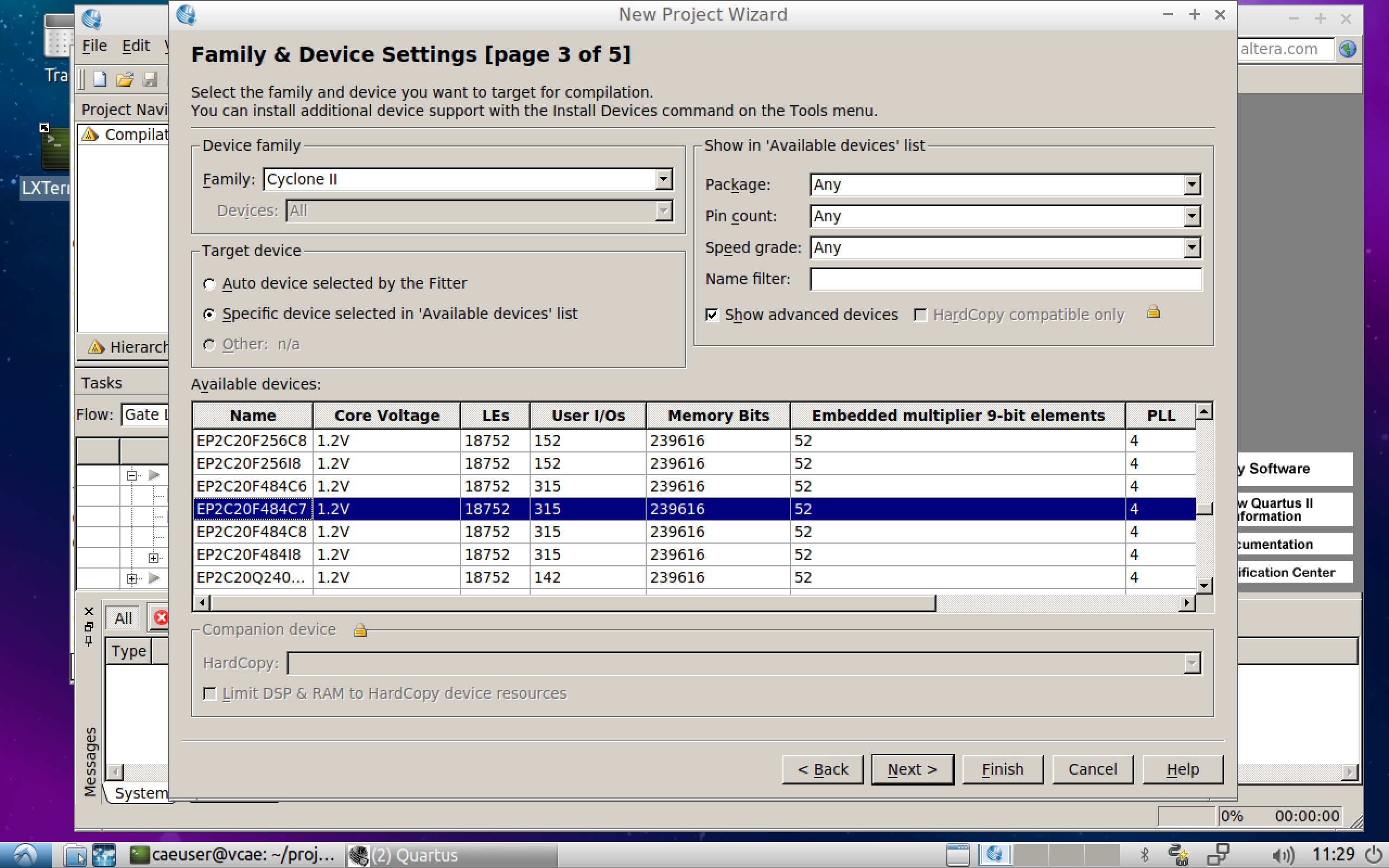

Danach muss der FPGA Typ auswählt werden, der sich auf der Platine befindet. Wählen Sie als Familie “Cyclone II” und als Baustein “EP2C20F484C7”.

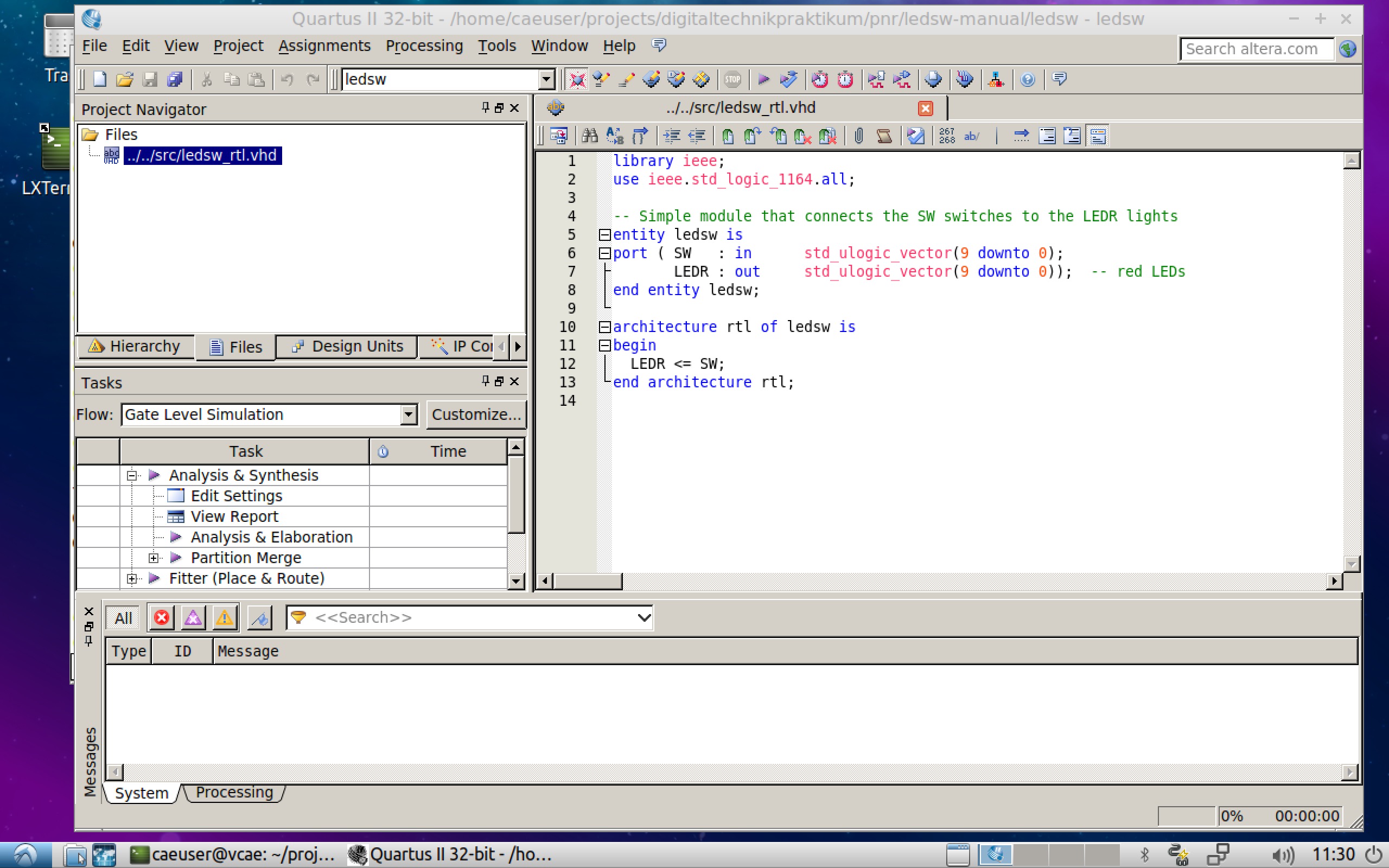

Danach können Sie beim Assistenten immer auf “Weiter” klicken und dann den Assistenten beenden. Das Projekt sollte dann so aussehen:

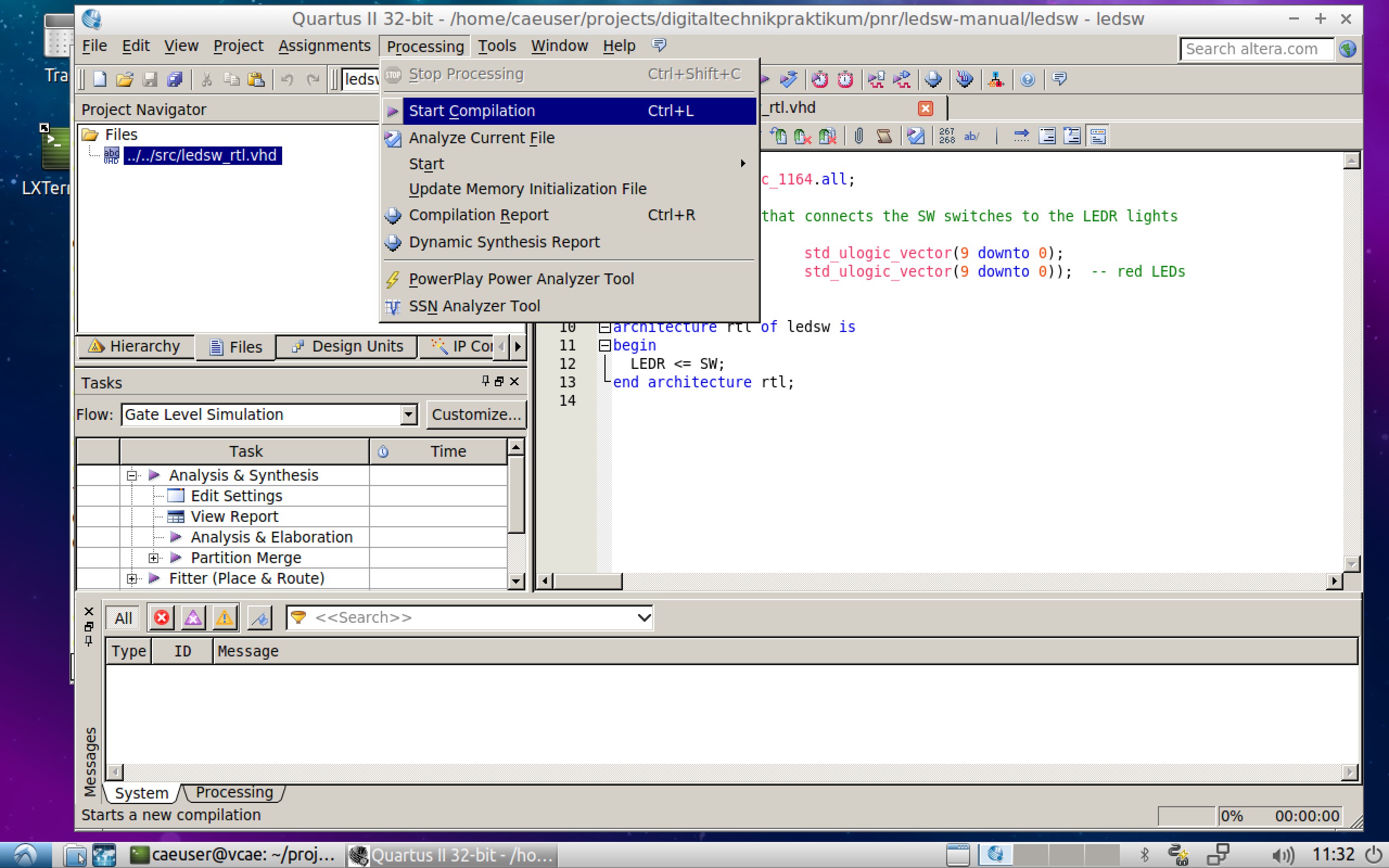

Starten Sie jetzt die Übersetzung der VHDL Datei mit “Processing → Start Compilation”.

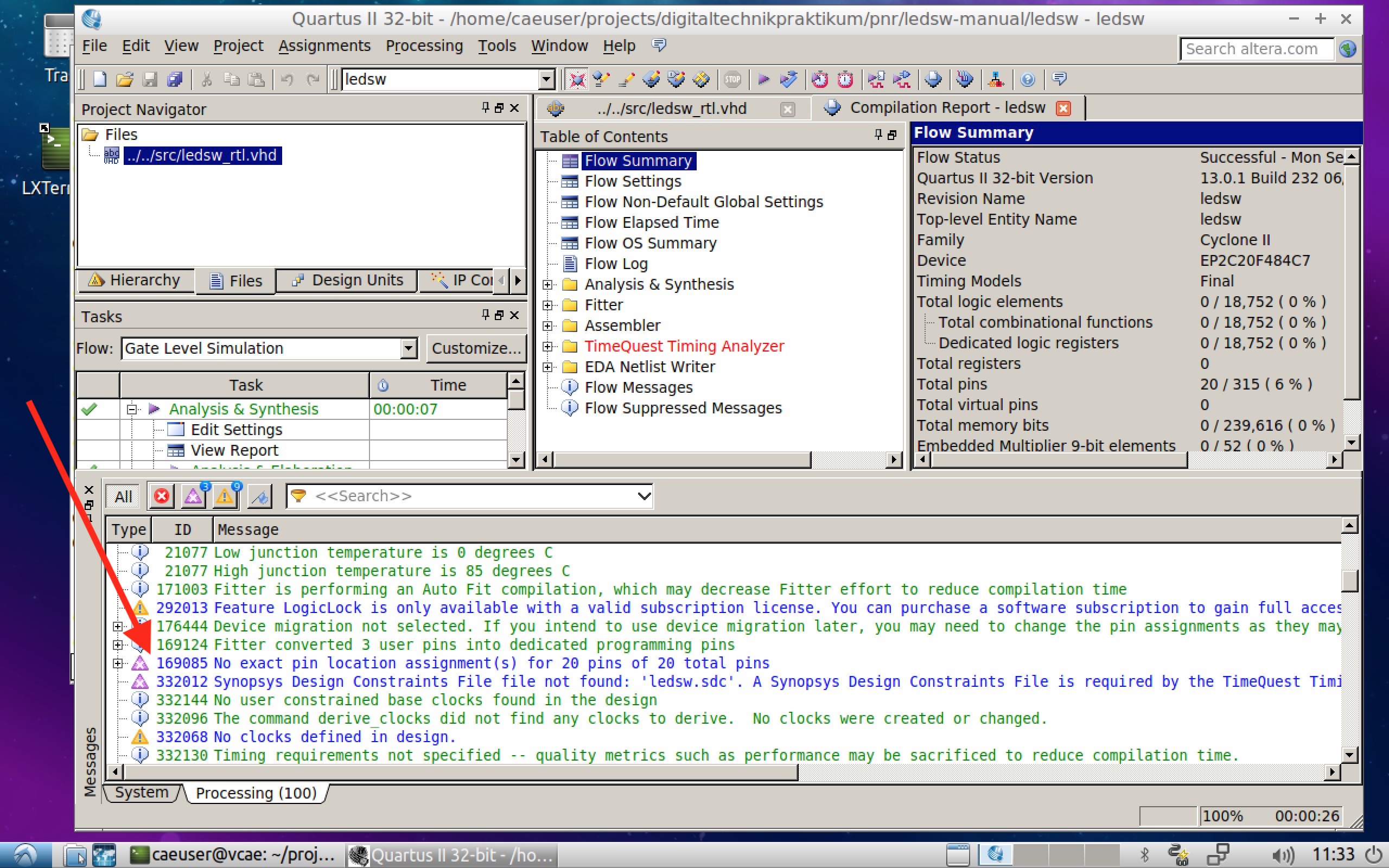

Die Synthese sollte durchlaufen. Allerdings treten zwei wichtige Warnmeldungen auf.

Die eine Meldung sagt aus, dass für Ein- und Ausgänge keine Pins auf dem FPGA festgelegt sind. Die andere Meldung besagt, dass alle ungenutzten Pins vom FPGA als “Output driving Ground” geschaltet sind. Das ist nicht gut, wenn an diesem Pin z.B. ein Schalter angeschlossen ist, der auf VDD geschaltet ist. Dann gibt es einen Kurzschluss.

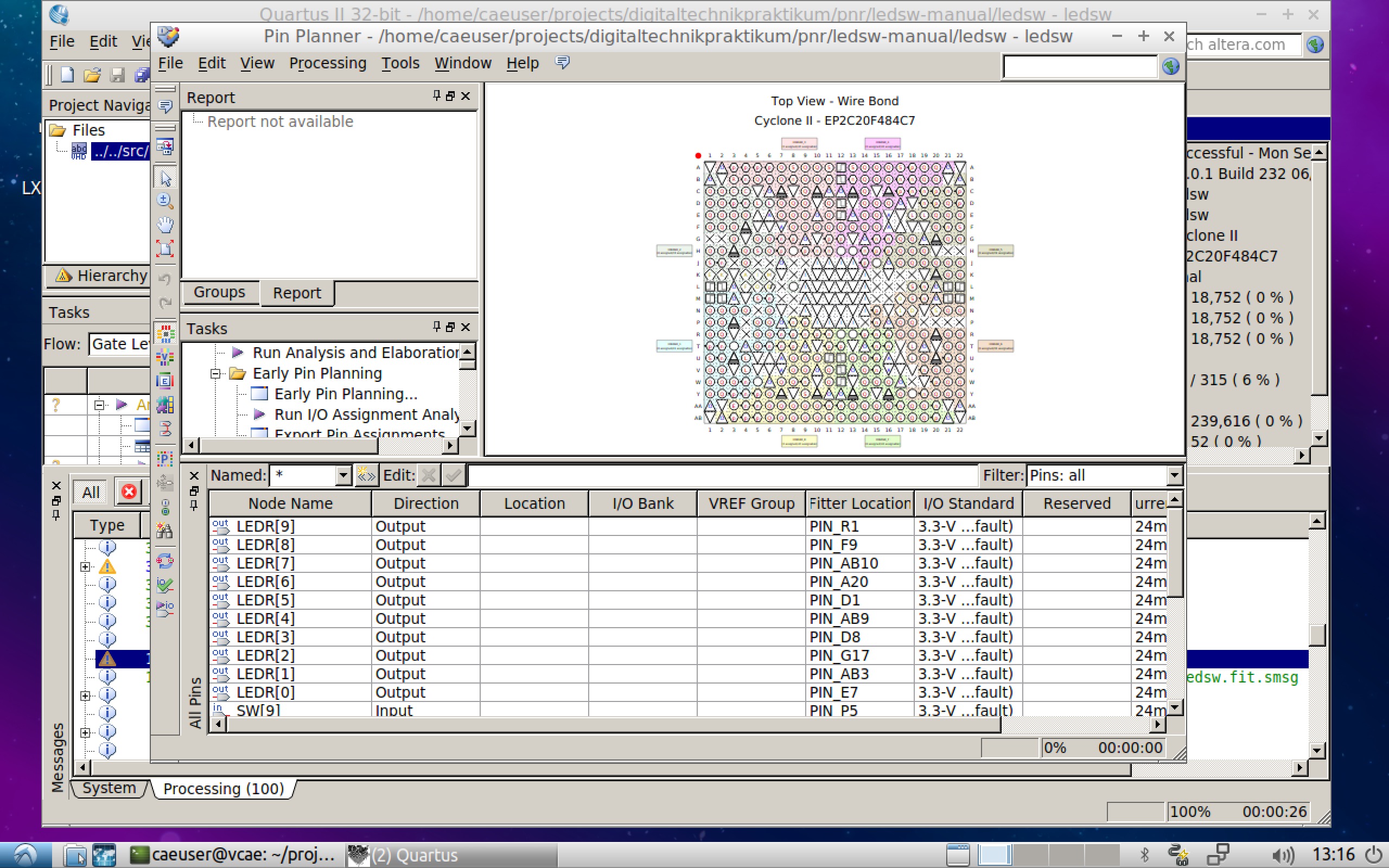

Man kann die nicht angeschlossenen Pins auch im “Pin Planner” anschauen.

Dort sieht man, dass für die Anschlüsse “LEDR” und “SW” noch keine Pinfestlegung erfolgt ist. Das “Location” Feld ist noch leer.

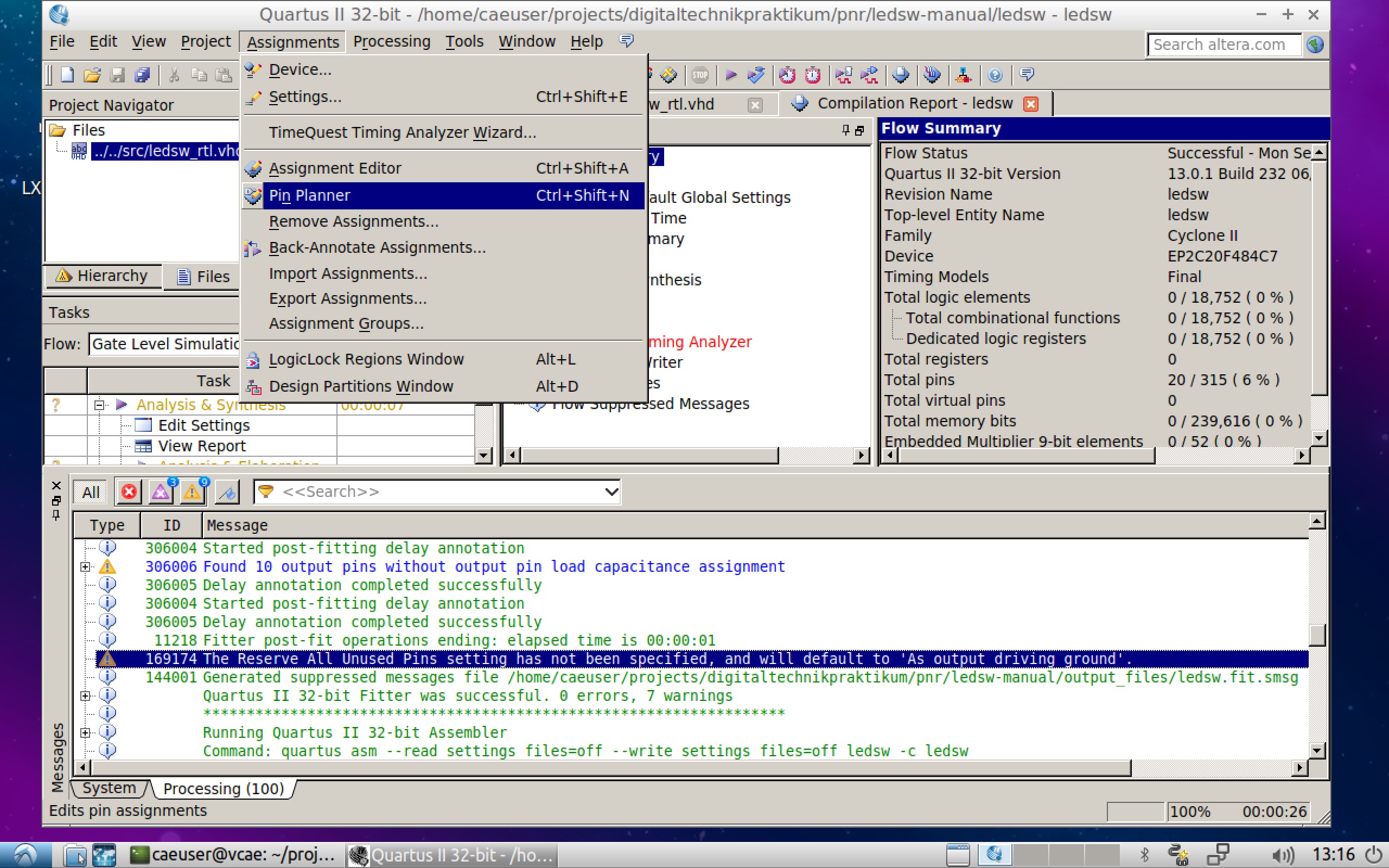

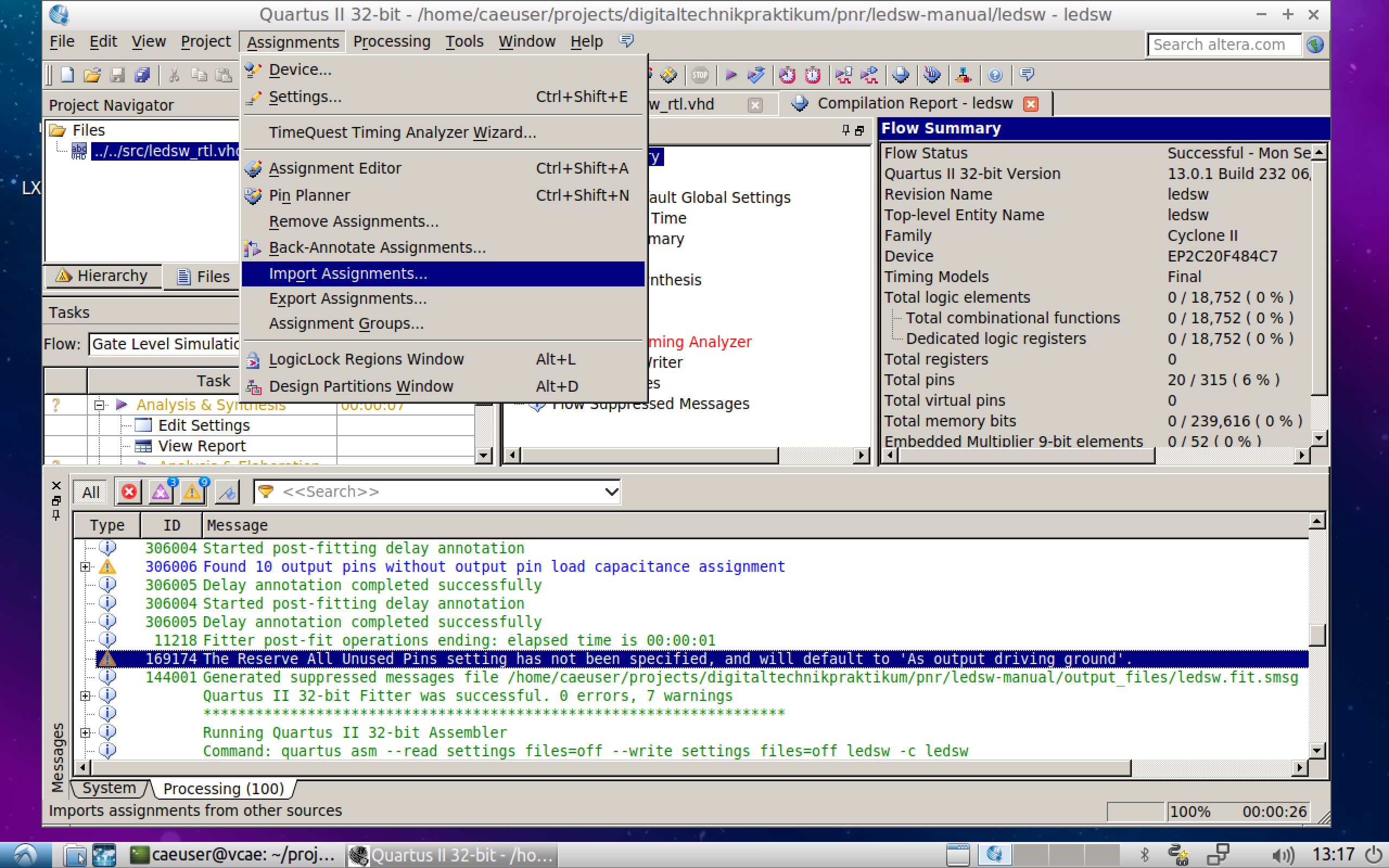

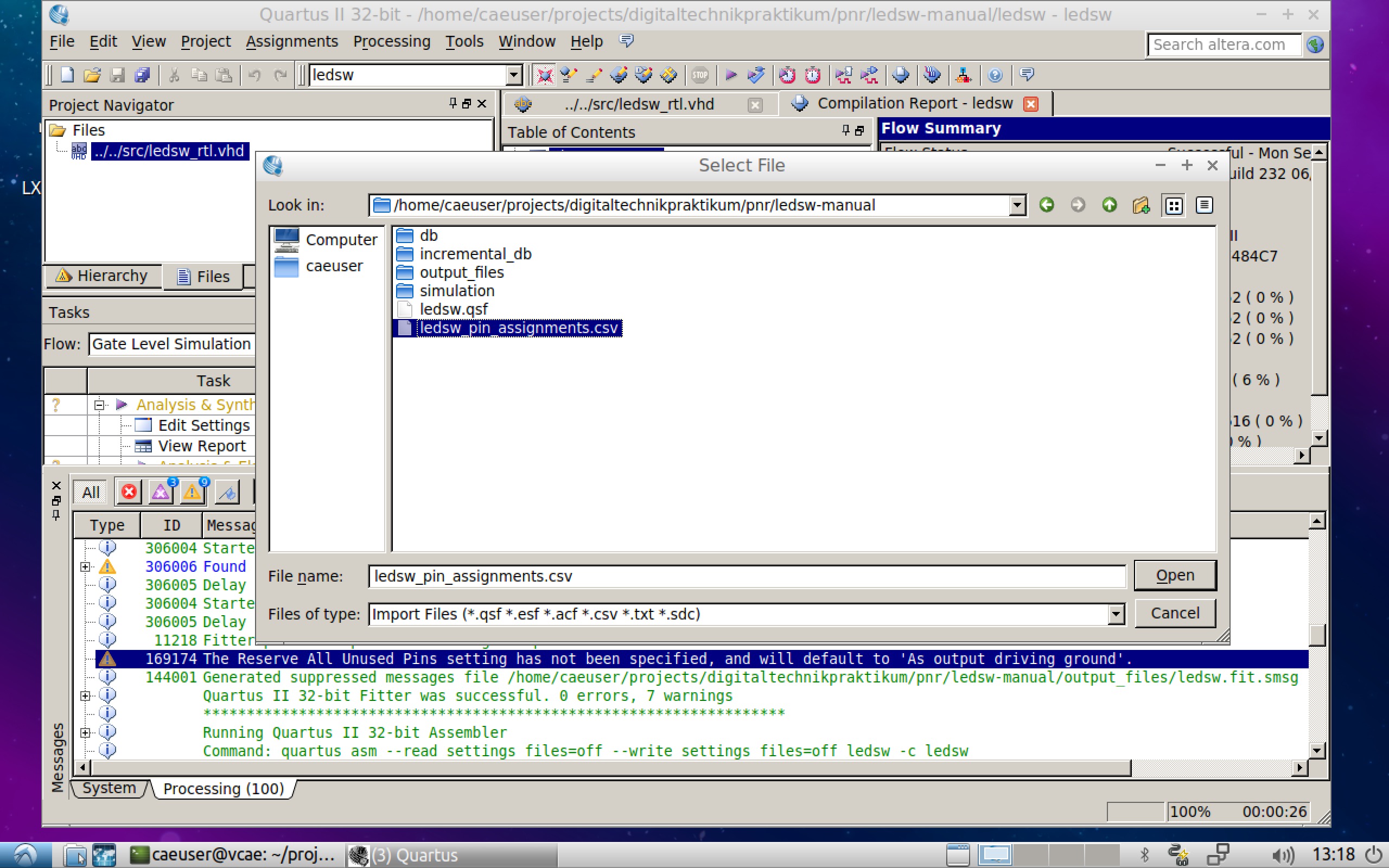

Um die Pins festzulegen wird jetzt mit “Assignments → Import Assignments” die Datei “ledsw_pin_assignments.csv” eingelesen.

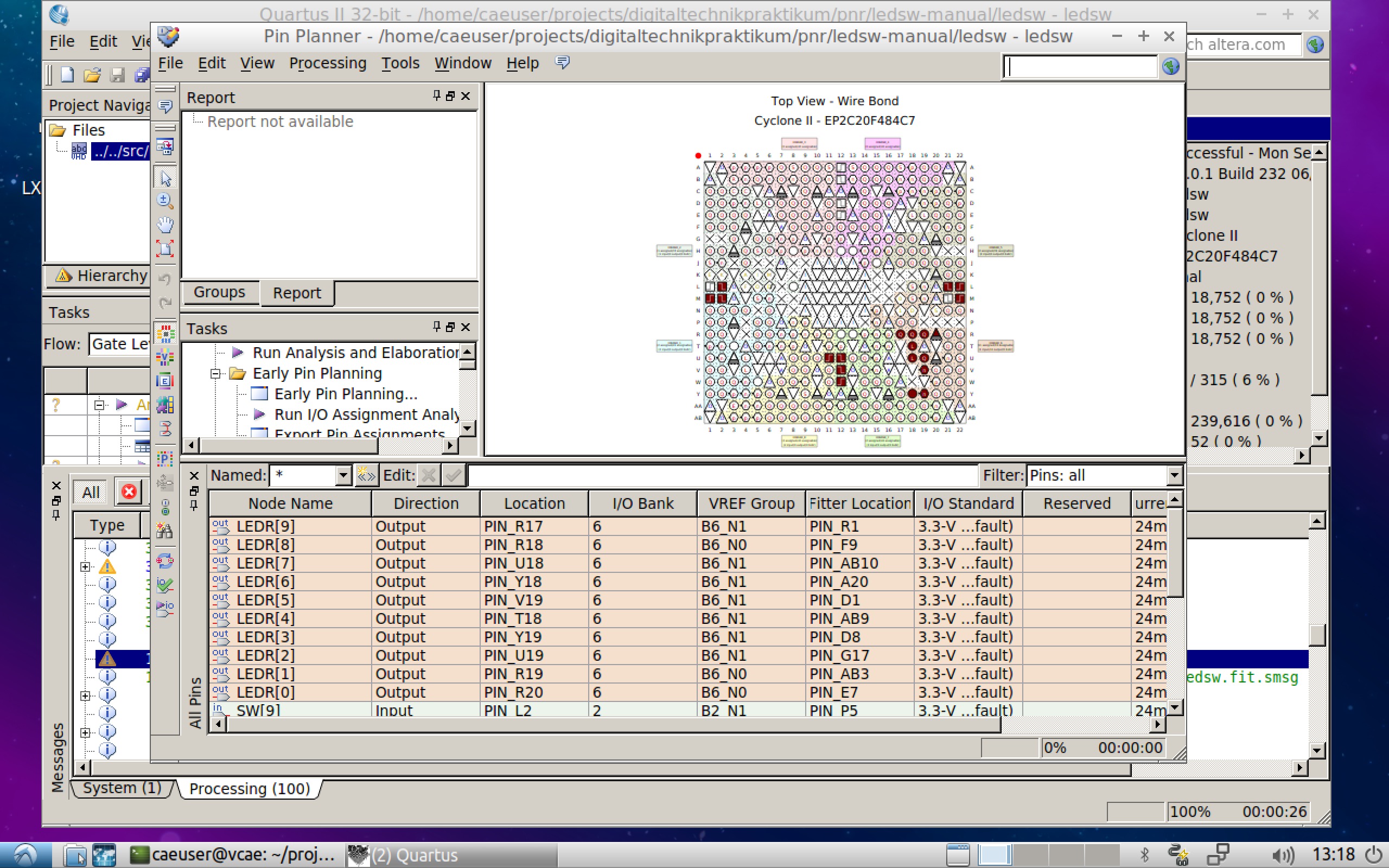

Wenn man dann den “Pin Planner” nochmal öffnet, sieht man die Zuordnung der Ein- und Ausgänge zu den Pins auf dem FPGA.

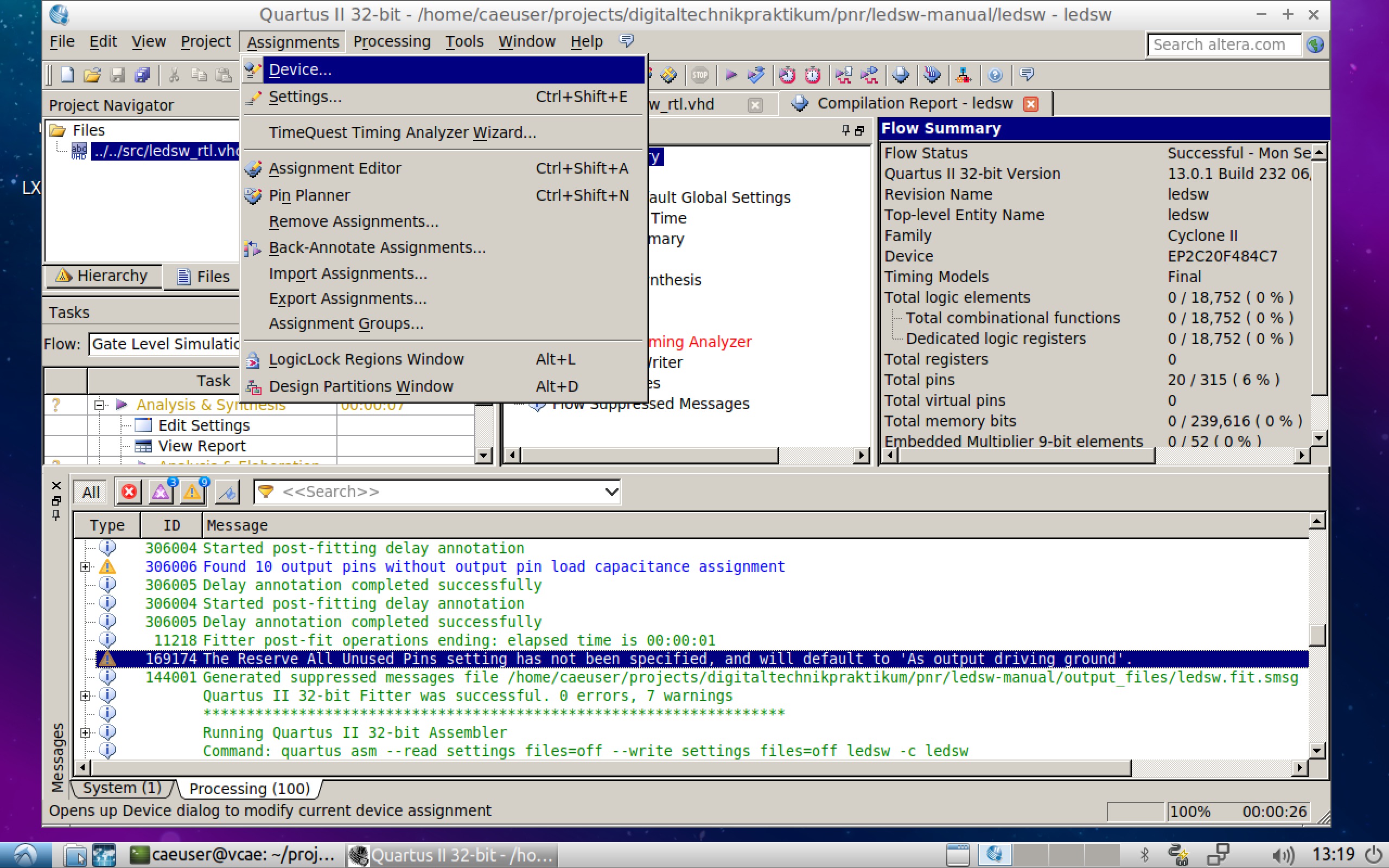

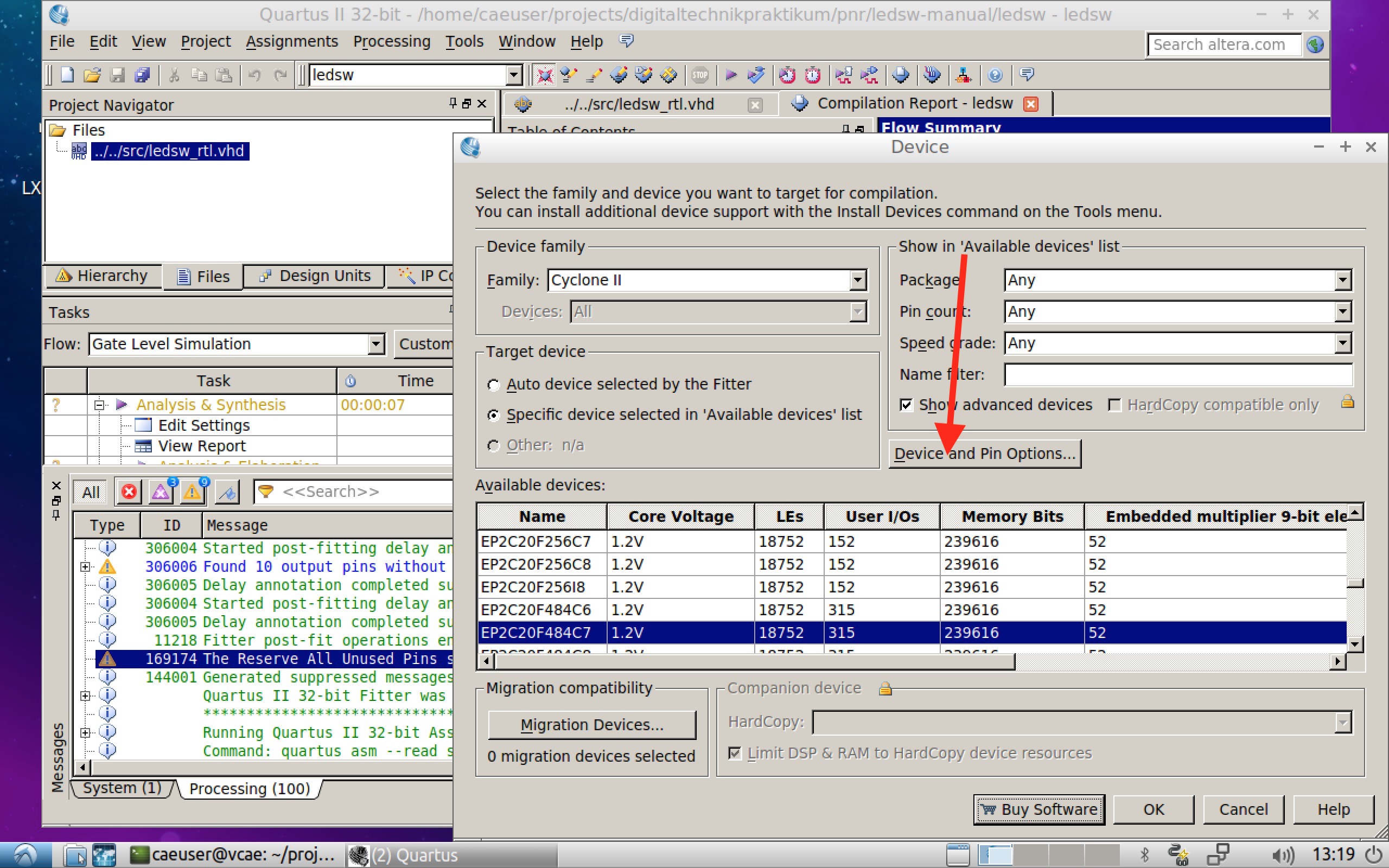

Jetzt muss noch festgelegt werden, dass unbenutzte Pins als Eingänge geschaltet werden. Wählen Sie dazu “Assignments → Device”.

und dann “Device and Pin Options”

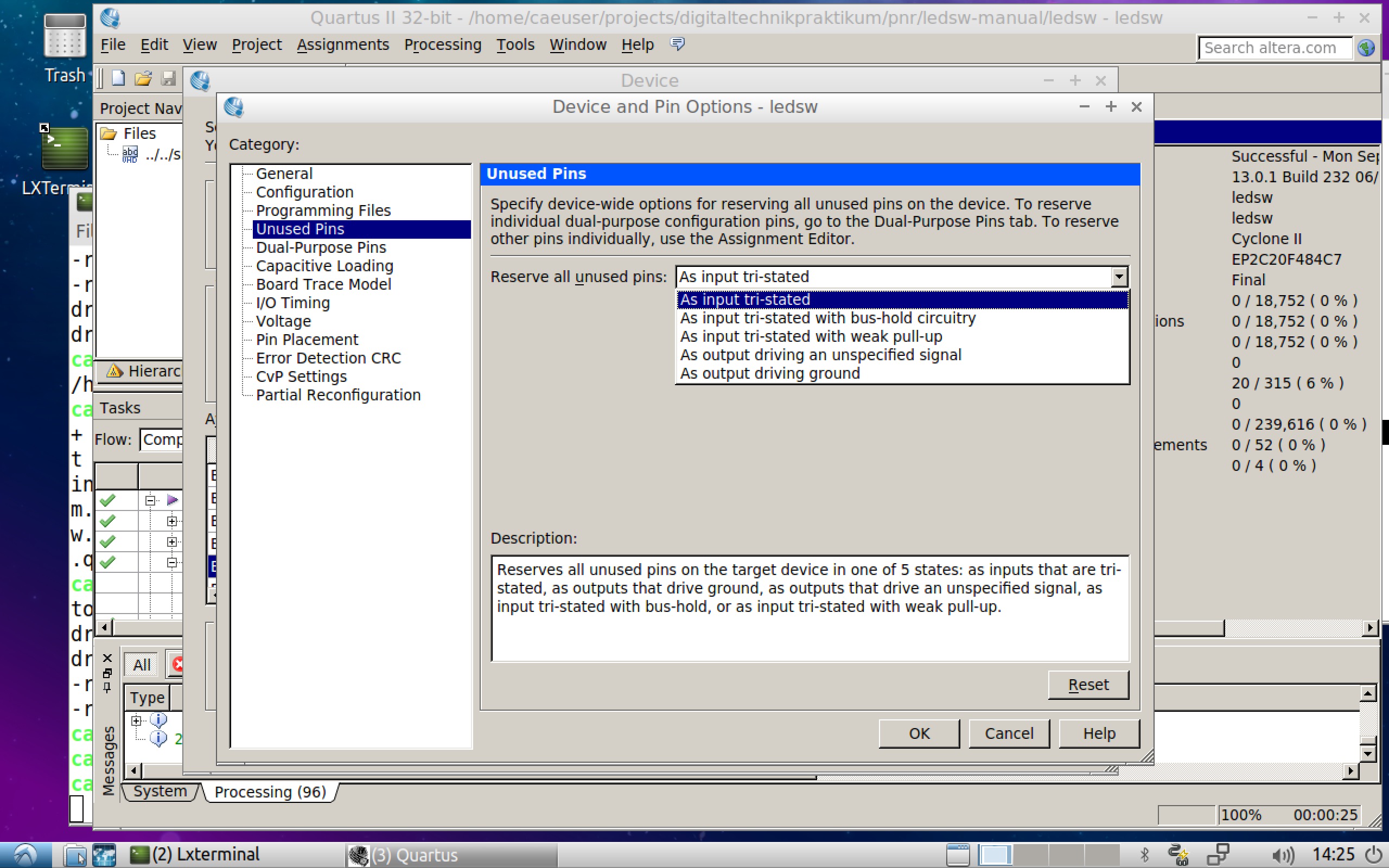

Wählen Sie dann bei “Unused Pins” die Option “As input tri-stated”.

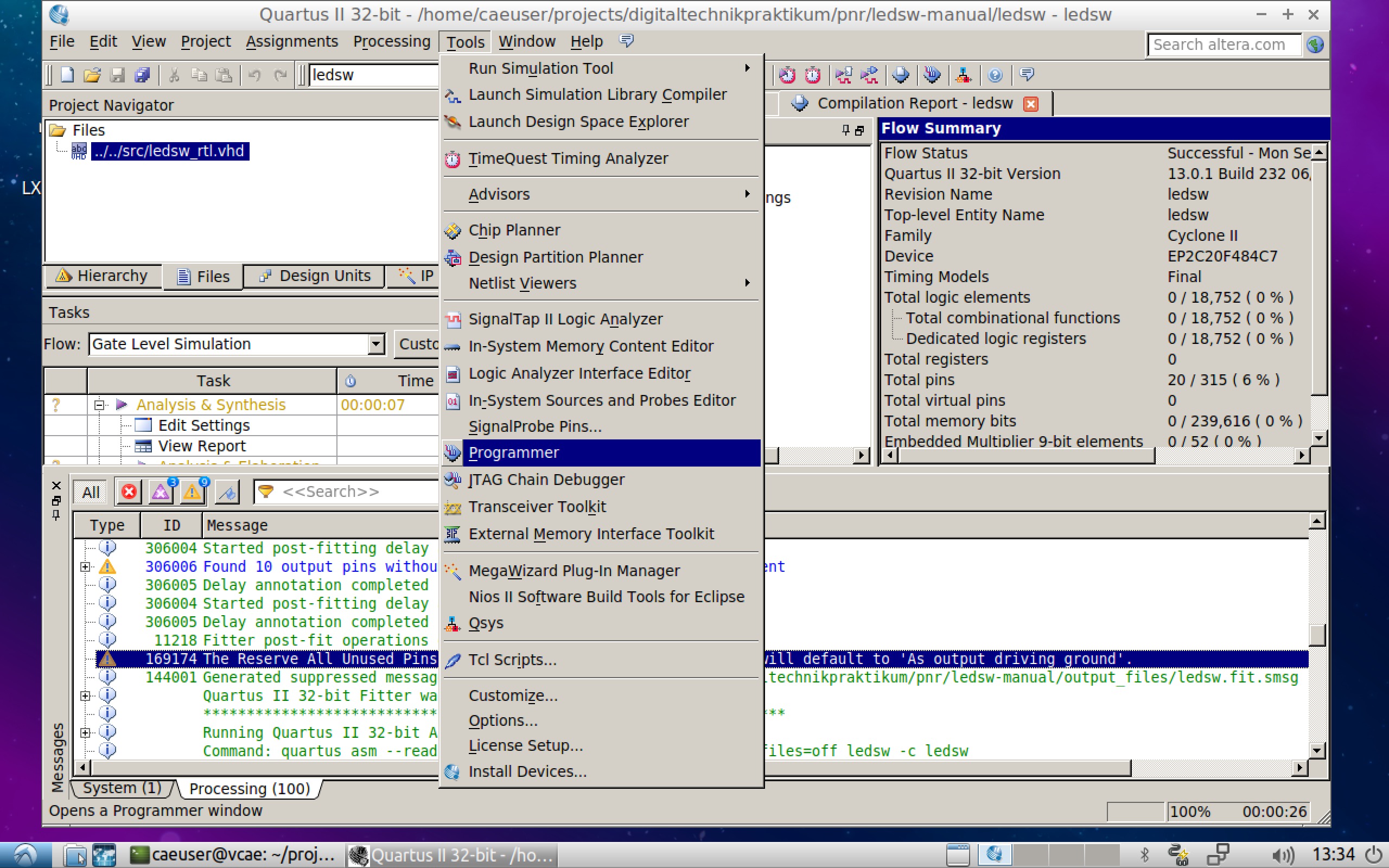

Sie müssen dann die Synthese nochmal neu starten mit “Processing → Start Compilation”. Nach erfolgreicher Synthese können Sie den “Programmer” starten mit “Tools → Programmer”.

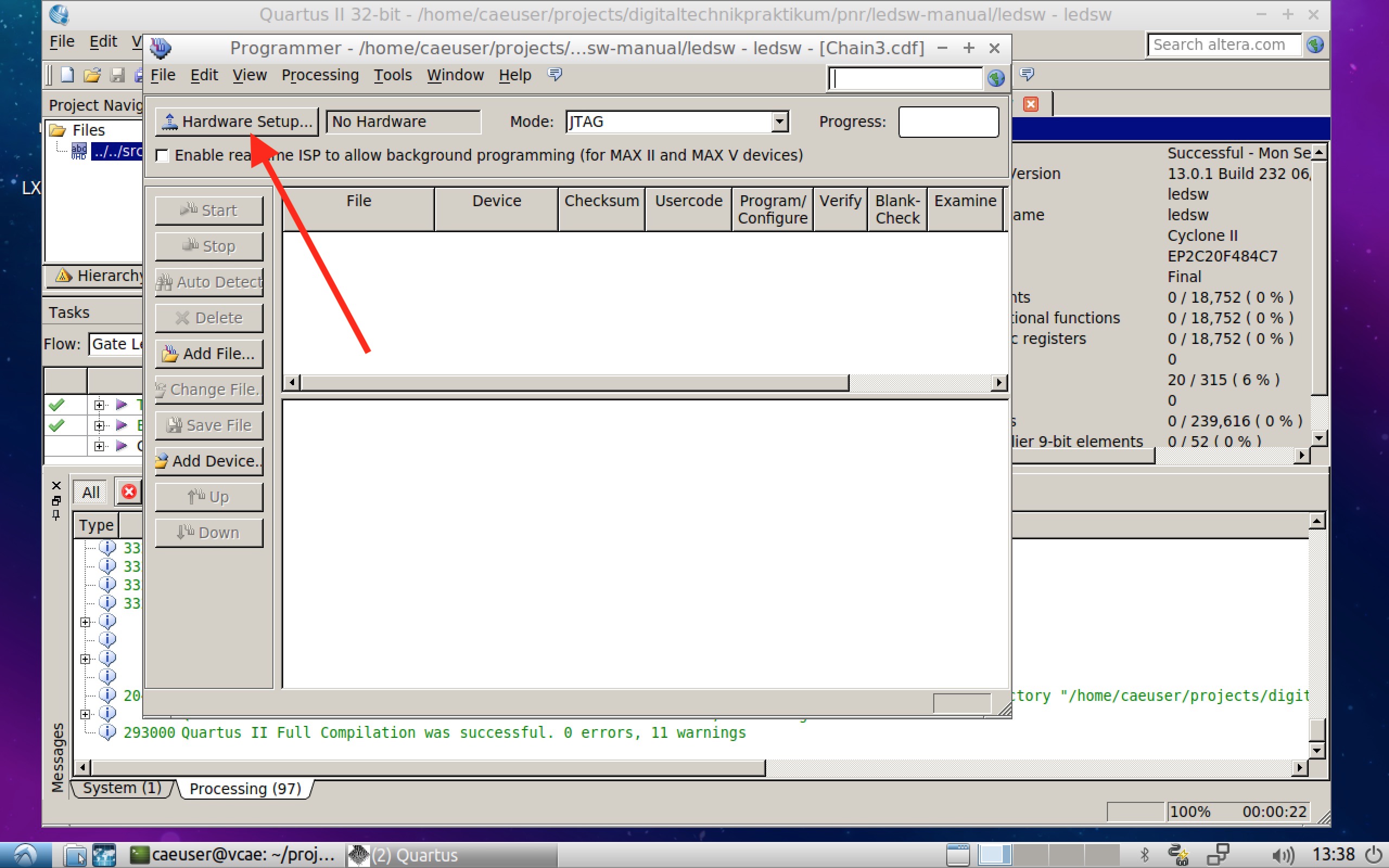

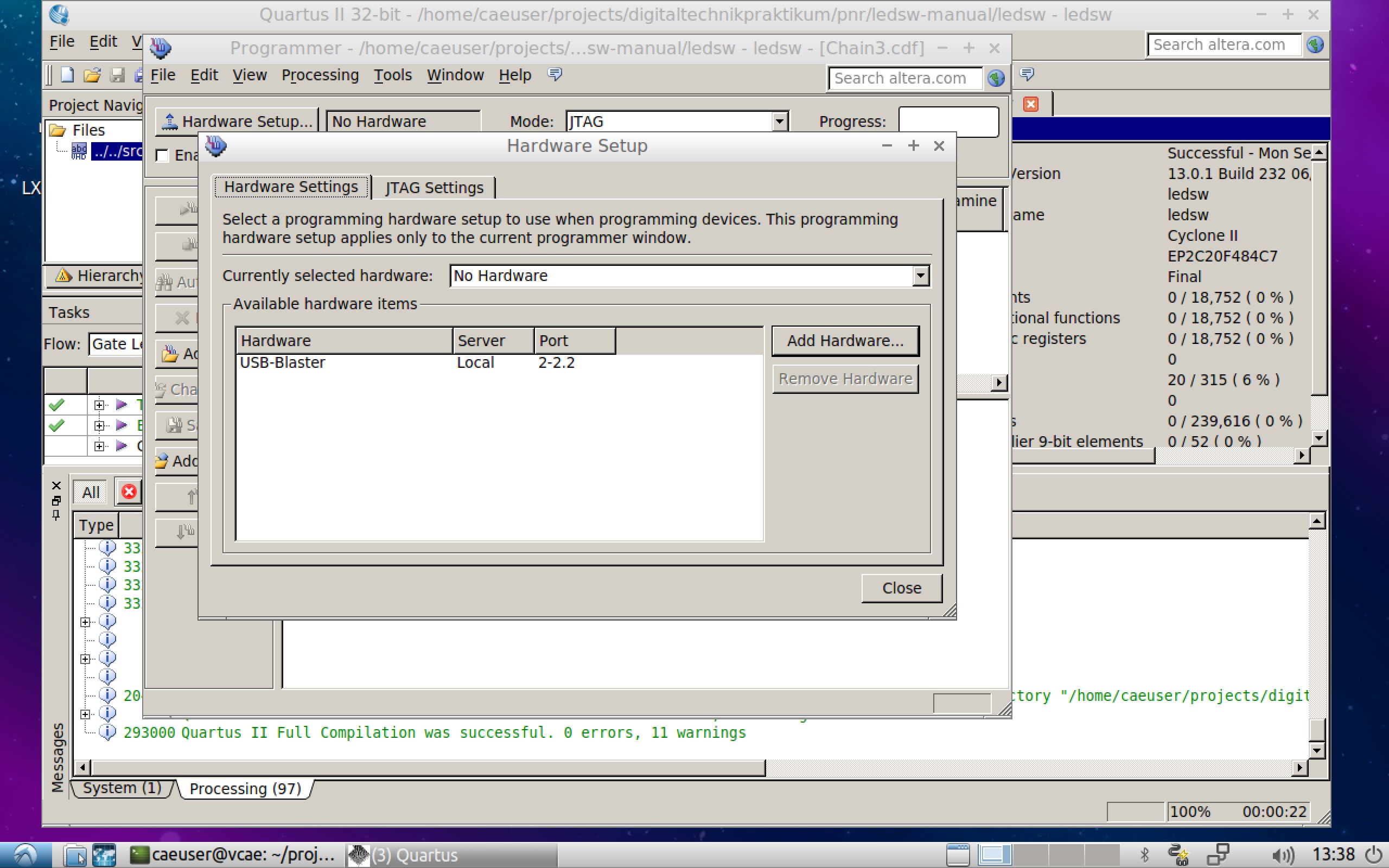

Im Programmer muss man dann die Programmierschnittstelle zur Programmierung des FPGA auswählen. Das funktioniert nur, wenn auch tatsächlich ein FPGA Board über USB am Rechner angeschlossen ist. Falls Sie mit einer virtuellen Maschine arbeiten, muss der USB Port der virtuellen Maschine zugeordnet werden.

Wenn das FPGA Board angeschlossen und die virtuelle Maschine richtig konfiguriert ist, dann kann man USB-Blaster [2-2.2] auswählen.

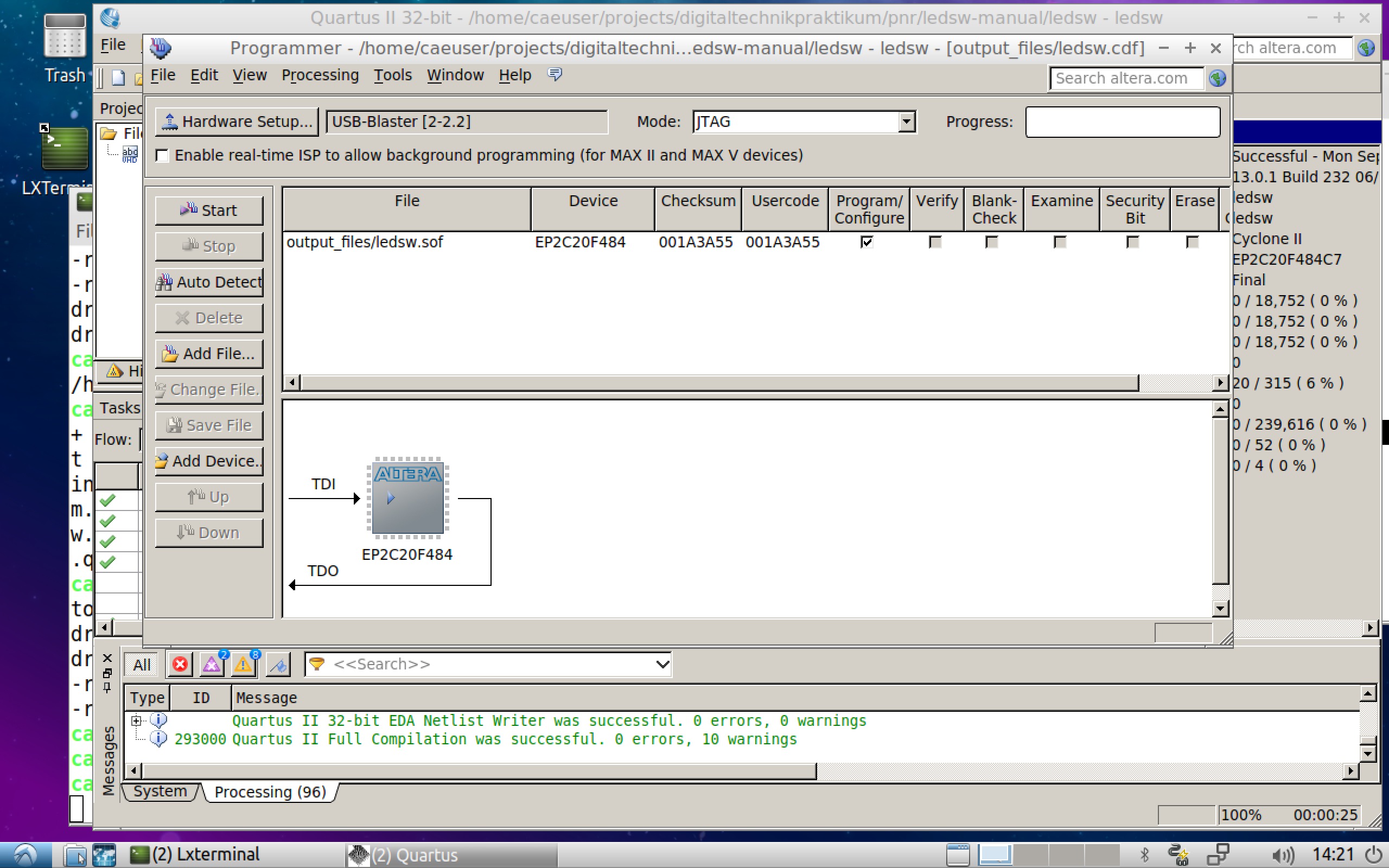

Nach dem Kompilieren steht die FPGA Konfigurationsdatei “ledsw.sof” zur Verfügung. Diese Datei muss man mit “Add File” auswählen. Danach kann man den Download der Konfigurationsdatei mit “Start” beginnen.

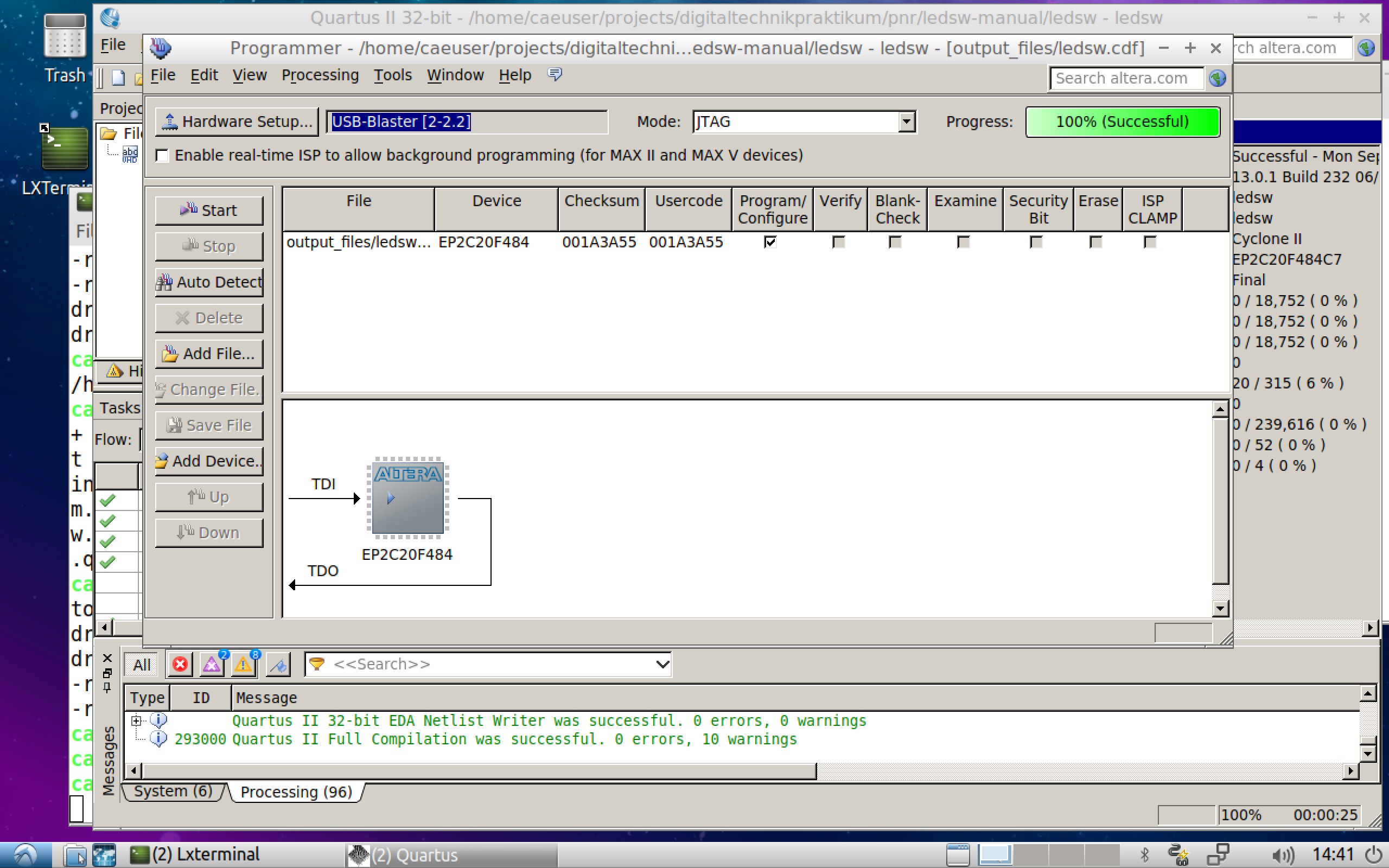

Wenn der Download erfolgreich war, dann sieht man das am grünen “Progress” Balken.

Danach kann man auf dem FPGA die roten LED's über die Schalter darunter ein- und ausschalten.

Synthese mit Altera Quartus - Projekt aufsetzen mit Skript

Alternativ zum Aufsetzen mit der interaktiven GUI kann man das Projekt auch mit einem Skript konfigurieren. Der Vorteil dieses Verfahrens ist, dass immer klar ist wie das Projekt konfiguriert wurde. Man kann zu jedem Zeitpunkt auf Basis der VHDL Dateien und der Skripte das Projekt neu aufsetzen. Jede einigermaßen professionelle Entwicklung nutzt deshalb Skripte als Basis. Eine häufig verwendete Skriptsprache für CAE Software ist tcl. Auch Altera verwendet tcl um die Verwendung der GUI zu vermeiden. Wechseln Sie in das Verzeichnis ledsw-scripted.

cd cd projects cd digitaltechnikpraktikum cd pnr cd ledsw-scripted

In diesem Verzeichnis befinden sich zwei tcl Skripten.

Erzeugen und Konfigurieren des Projektes

Das Skript create_quartus_project_settings.tcl sorgt für die folgenden Schritte beim Aufsetzen des Quartusprojektes.

- Konfigurieren des Projektnamens

- Festlegen des FPGA Typen

- Hinzufügen der VHDL Dateien

- Konfigurieren der Pins

Das Skript wird ausgeführt mit:

quartus_sh -t create_quartus_project_settings.tcl

Nachdem das Skript gelaufen ist, befindet sich in dem Verzeichnis die Quartus Projektdatei “ledsw.qpf”. Sie können das Projekt mit der Quartus GUI anschauen mit:

quartus ledsw.qpf

Starten der Synthese

Das Skript quartus_project_flow.tcl sorgt für die Schritte

- Analyse und Elaborieren des VHDL Codes

- Starten der Synthese und Fitting auf das FPGA

- Erzeugen des Synthesereports “flowsummary.log”

Starten Sie das Skript mit

quartus_sh -t quartus_project_flow.tcl

Nach diesem Schritt befindet sich im Verzeichnis die Datei “flowsummary.log” mit dem Synthesebericht und die Datei “ledsw.sof”. Die sof Datei ist die Konfigurationsdatei für das FPGA, die jetzt mit dem Programmer auf das Board geladen werden kann.

Download der FPGA Konfigurationsdatei mit dem Programmer

Danach können Sie das Board programmieren mit

quartus_pgm -c USB-Blaster --mode jtag --operation="p;ledsw.sof"

Jetzt können mit den Schaltern “SW” die roten Leuchtdioden auf dem Board an- und ausgeschaltet werden. Die Variante mit dem Skript kommt ohne GUI aus. Allerdings ist es nicht notwendig jedesmal wenn sich beispielsweise der Code in der VHDL Datei geändert hat auch das Projekt komplett neu aufzusetzen. Das gezielte Ausführen der jeweils notwendigen Skripten wird mit dem im folgenden beschriebenen Make basierten Verfahren gewährleistet.

Synthese mit Altera Quartus - Make basiert

Nach der skriptbasierten Synthese der Schaltung wird jetzt die endgültige Variante basierend auf dem Tool “make” eingeführt. Alle folgenden Projekte werden mit make aufgesetzt. Das Verfahren mit make ist ähnlich dem Verfahren mit den Skripten - auch bei Make werden solche Skripte aufgerufen. Bei dem Skriptverfahren gibt es zwei Skripte. Ein Skript erstellt das Projekt und ein Skript startet die Synthese. Für das Tool make gibt man in einer Datei “makefile” an welche Dateien von einem Skript erzeugt werden und welche Dateien für den Schritt gebraucht werden (die Abhängigkeiten). Make überwacht dann diese Abhängigkeiten und wenn sich irgendeine Datei ändert (z.B. eine VHDL Datei), dann ruft make alle notwendigen Schritte auf um das Projekt zu aktualisieren.

Die makefiles im Digitaltechnikpraktikum sind aufgeteilt. Es gibt jeweils ein makefile pro Projekt und ein makefile für alle Projekte, da die meisten Schritte in jedem Projekt gleich sind und sich nur die VHDL Dateien und die Pins vom FPGA ändern.

Wechseln Sie in das Verzeichnis “digitaltechnikpraktikum/pnr/ledsw-make”.

cd cd projects cd digitaltechnikpraktikum cd pnr cd ledsw-make

In diesem Verzeichnis ledsw-make befinden sich zwei Dateien. Die Datei makefile enthält die Informationen für das Tool “make”. Die Liste der VHDL Dateien für die Synthese wird aus der Datei ../../sim/ledsw/makefile.sources aus dem Simulationsverzeichnis geladen. Danach wird das allgemeine makefile für alle Syntheseprojekte pnr/makefile mit “include ../makefile” geladen.

In diesem pnr/makefile sind verschiedene “Targets” angegeben. Targets können Dateien oder Namen sein. Ein Target ist beispielsweise die Datei “flowsummary.log”. In Zeile 40 steht, dass das Target “flowsummary.log” abhängt von der Quartusprojektdatei ledsw.qpf und dem Skript ../../scripts/quartus_project_flow.tcl. Die Datei ledsw.qpf ist wieder ein eigenes Target. In Zeile 28 steht das “ledsw.qpf” von den VHDL Dateien, von dem Skript create_quartus_project_settings.tcl und der Pinkonfigurationsdatei ledsw_pins.tcl abhängt. In den folgenden Zeilen 29 bis 35 steht, wie die Projektdatei ledsw.qpf erzeugt wird. Daneben gibt es noch “PHONY Targets” wie z.B. qproject. Dieses Target hängt von ledsw.qpf ab.

Um ein Target zu erzeugen muss man make aufrufen. Wenn man kein Target angibt, wird das erste Target genommen, dass gefunden wird. Das ist hier “help” und zeigt die möglichen Targets an.

make

Um das Quartusprojekt zu erzeugen, muss man make mit dem Target “qproject” aufrufen.

make qproject

Man sieht wie jetzt quartus mit dem Skript zum Erzeugen eines Projektes gestartet wird. Der Sinn von make wird deutlich, wenn man danach “make qproject” ein zweites Mal aufruft.

caeuser@vcae:~/projects/digitaltechnikpraktikum/pnr/ledsw-make$ make qproject make: Nothing to be done for `qproject'.

Das Programm make hat erkannt, dass das Projekt schon erzeugt ist und neuer ist als alle abhängigen Dateien. Deshalb muss quartus nicht noch einmal gestartet werden, denn das Projekt ist aktuell. Wenn Sie jetzt beispielsweise die Datei “ledsw_pins.tcl” ändern und nochmal “make qproject” starten, dann wird Quartus wieder gestartet um das Projekt neu zu bauen. Sie können das ausprobieren wenn Sie mit dem Programm “touch” die Datei “leds_pins.tcl” mit einem neuen Änderungszeitstempel versehen, so als ob Sie die Datei geändert hätten.

touch ledsw_pins.tcl make qproject

Mit “make clean” können alle erzeugten Dateien gelöscht werden. Mit “make prog” wird die Belegungsdatei ledsw.sof auf das FPGA geladen. make sorgt dafür, dass alle notwendigen Schritte (Projekt konfigurieren / Synthese starten) vorher ausgeführt werden. Mit

make quartus

wird das Projekt erzeugt und Quartus mit der graphischen Benutzeroberfläche gestartet.